| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

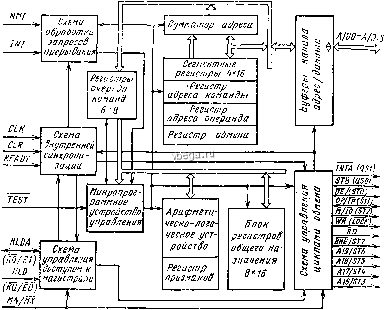

Космонавтика Конструирование интегральных микросхем Устройство управления представляет собой комбинационную му, которая на основании входных управляющих сигналов форм ет внутренние управляющие сигналы, которые обеспечивают сле щие режимы работы микросхемы: начальная установка; пряма, редача; генерация контрольных бит; обнаружение ошибки; коррс ошибки; диагностика обнаружения ошибки; диагностика корре ошибки; внутреннее управление. Назначение выводов КМ1804; приведено в табл. 3 68. 3.3. Микропроцессорный комплект серии ИР1810 1Микропроцессорный комплект серин КР1810 представляет собой дальнейшее развитие МПК серии КР580 и на уровне ассемблера программно совместим с этой серией. Однако он является 16-разряднь1м обладает более высоким быстродействием н имеет ряд функциональных особенностей, позволяющих строить на его основе мощные вц-сокопронзводительные и мультипроцессорные системы. Собственно микропроцессор (микросхема КР1810ВМ86) выпо.-,-нен по НМОП-технологии, контроллер прерываний (микросхема КР1810ВН95А) - по пМОП-технодогии, остальные микросхемы, вхо-дяш.ие в МПК серии КР1810, выполнены по биполярной технологии ТТЛШ. Все микросхемы комплекта имеют один источник питания -г5 В±5 %. Диапазон рабочих температур -10... + 70°С. Ниже приведены состав МПК серии КР1810 и основные характеристики входящих в него микросхем. Центральное процессорное устройство КР1810ВМ86 Разрядность арифметического устройства . . 16 Разрядность совмещенных шин адреса/данных 20 16 Объем адресуемой памяти, Мбайт..... 1 Число базовых команд......... 135 Число адресуемых устройств ввода/вывода . 2 /2 Число режимов адресации......., 24 Число внутренних 16-разрядиых регистров: общего назначения.......... 4 индексных............. 2 указателей ............. 2 сегментных............. 4 Число внешних запросов прерывания , , . 2 Число впутрепних программных запросов пре- рпвания............... 3 Число уровней прерывания....... 256 Частога тактовых сигналов, МГц..... <5 Время выполнения команд типа регистр-регистр, мкс: пересылка............. <0,4 сложение............. <0,6 умножение............, 23,6-26,6 деление.............. 28,6-32,4 Потребляемая мощность, мВг....., <2100 Генератор тактовых импульсов КР1810ГФ84 Максимальная частота входного тактового сигнала пли опорного генератора, МГц .... <25 Частота выходных тактовых пМОП-сигналов F/3 Частота выходных тактовых ТТЛ-сигналов . F/6 Потребляемая мощность, мВт...... <735 Контроллер шины КР1810ВГ88 Число разрядов шипы состояния ..... Частота тактовых сигналов, МГц..... <10 Потребляемая мощность, мВт...... <!150 Арбитр шины КР1810ВБ89 Число разрядов шины состояния..... 3 Число режимов работы......... 4 Число методов разрешения приоритета ... 3 Частота тактовых сигналов, МГц..... <10 Потребляемая .мощность, мВт...... <865 Программируемый контроллер прерываний KPt8!0BH59A Число обслуживаемых запросов прерывания . 8 Разрядность шины данных........ 8 Число программируемых режимов работы . . 3 Время выдачи сигнала Прерывание на сигнал Запрос , НС........... <350 Потребляемая мотщиость, мВт...... <450 Микросхемы сеоии КР1810 выполнены в пластмассовых корпусах типа- 2I04.l8-5 - КР1810ГФ84; 2140.20-1 - КР1810ВГ88, КР1810ВБ89; 2121.28 5 - КР1810ВН59А; 2123.40-2 - КР1810ВМ86. 3.8,1. Микросхема КР1810ВМ86 Микросхема KP1810BMS6 представляет co6oi i однокристальный высокопроизводительный 16 разрядный микропроцессор. Система команд микропроцессора КР1810ВМ86 совместима с системой команд микропроцессора КР580ВМ80А иа языке ассемблера. Высокая производительность микропроцессора КР1810ВМ86 обеспечивается благодаря совметцению выполнения операций обработки и обращения, что достигается использованием б юка предварительной выборки команд Особенностью микропроцессора КР1810ВМ86 является возможность работы в двух режимах: минимальном и максимальном. Минп-мальный режим используется в системах, имеющих несложную кон-фт.гурацию. При этом микропроцессор сам вырабатывает все необходимые сигналы управления периферийными устройствами. Максимальный режим применяется при использовании микропроцессора в составе снс-1емы сло.жной конфигурации. В этом случае используется сттециальная микросхема - контроллер шины КР1810ВГ88, которая анализирует сигналы состояния микропроцессора STO-ST2 и в зависимости от их значения формирует соответствующие сигналтл 18* 275  Рис. 3.63. Структурная схема КР1810ВМ86 управления периферийными устройствами. Установка минимального и.ы м-1ксима.!ьно10 рржьма работы микропроцессора осуществляется поцключением входа MN/MX соответственно к выводу Ucc или GND. Архитектурной особенностью микропроцессора КР1810ВЛ186 является способность координировать в.эаимодействие нескольких процессоров, что позволяет строить на его основе мультипроцессорные системы В этих системах возможно нрименение двух типов процессоров: независимых, т. е. выполняющих собственный поток команд, и вспомогательных (сопроцессоры). Сопроцессор просматривает команды, выбираемые главным процессором, признает некоторые из них своими и выполняет их. Микросхему КР1810ВМ86 можно ис-по.щзовать в ка1естве независимого процессора, а в роли сопроцессоров могут выступать специальные процессоры ввода/вывода, обработки данных и др (КМ1810ВМ89, КМ1810B,V187), Структурная схема КР!8!0ВМ86 представлепа на рис. 3.63. Ариф\ етпческо-логическое устройство выполнено на базе комбинационного 16-разрядного сумматора с последовательно-паралле п-.-ным переносом и трех временных регистров для промежуточного хранения операндов и результата операции. Выход АЛУ связан с регистром признаков (PST), в котором происходит запоминание специфических свойств результата арифметических и логических операций мик[юпроцессора, разрешение прерывания, пошаговый режим. При вьшолнении ряда команд в зависимости от состояния определен-

|