| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

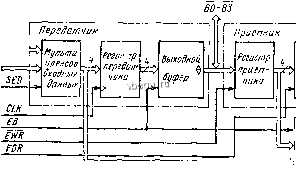

Космонавтика Конструирование интегральных микросхем \ Передатчик OR vPynbmu-пренсор дшшых Регистр чика ВО-ИЗ Выхвд.чзй буфер - PlpueniiUK Регистр приеп-пика .ЕыхоВмй Вуфер \DBO-B/ij Рнс. 3.53. Структурная схема КМ1804ВА1 жения высокого уровня. Приемник микросхемы КМ1804ВА1 состжт из 4-разрядного регистра, выполненного на D-триггерах типа .Защелка , и выходного буфера приемника, имеющего иа выходе состояние Вьп{Лючено . Управление приемом и хранением информации, поступа.ющой в регистр приемника по двунаправленной шине В, осуществляется сигналом EWR Разрешение записи . При низком уровне сигнала EWR информация с выводов ВО-ВЗ через регистр приемника и его выходной буфер передается на выходы DRO-DR3. При высоком уровне сигнала EWR информация, поступившая на шнну В, запоминается в регистре приемника и хранится в течение всс-о времени, пока на выводе EWR присутствует сигнал высокого урси-ня. Управление выходньпу! буфером приемника осуществчяется сиг};;-лом EDR Разрешение шины DR . При подаче на вход EDR напряжения высокого уровня выходы DR уставав тиваются в состояи.! Выключено Передача информации с шин DA и DB на В и с щт-ны В на DR осуществляется с инверсией. Назначение bubo-vB K.M1804BAi приведено в табл. 3.58. Табл и ц а ? 38

3.7.10. Микросхема КМ1804ВА2 Микросхема КМ1804ВА2 представляет собой 4-разрядный канальный приемопередатчик и выполняет те же функции в микропроцессорных системах, что и микросхема КМ!804ВА1. Структурная схема KMI804BA2 представтена на рис 3.54. Микросхема КМ1804В.А2 в отличие от микросхемы КМ1804ВА1 имеет одну шину входных данных DA и схему генерации бита контроля четности В зависимости от режима работы приемопередатчика, определяемого состоянием входа ЕВ Разрешение шины В , схема генерации бита контроля четности передает на выход М2 Признак сумму по mod 2 входных сигналов регистра передатчика (прн ЕВ = 0) или сумму по mod 2 выходных сигналов приемника (при ЕВ=1). В остальном работа микросхемы КМШ04ВА2 аналогична работе мик-.....лзначенпе выводов К.\П804ВА2 приведено росхемы K.M1804BAI. в табл. 3 59 Таблица 3.59

Передатчик ЛАо-т Регистр пгредатчикй БО-ВЗ Выходнойй буфер Приепнак Регистр р приемника BR0-BR3  Схема генерации бита контроля четности Рис. 3.54. Структурная схема КМ1804ВА2 17-300 3.7.11. Микрослема КМ1804ВАЗ Микросхе.ма КМ1804ВАЗ представляет собой 4-разрядпый приемопередатчик, предиазначеиный для применения в микропроцессорных системах в качестве буферного устройства для приема, хранения и передачи инЬормации, Структурная схема КМ!804В,\3 представлена на рис. 3.55. Микросхема состоит из 4-разрядного передатчика и 4-разрядного приемника. Входные данные, подаваемые на шину DA или DB через мультиплексор входных данных, управляемый сигналом SED, поступают в регистр передатчика. Прн низком уровне напряжения на входе SED производится передача данных с шнны DA, при высоком - с шины DB. Регистр передатчика выполнен на триггерах D-типа, запись информации в которые осуществляется но положительному фронту тактового сигнала CLK. Выходы D-триггеров через буферы, и.мсю-щне состояние Вык.ночено , подсоединены к двунаправленной шине В Перевод выходных б)-феров передатчика в состояние Выключено осуществляется прн поступлении на вход ЕВ Разрешение шины В сигнала высокого уровня. Регистр приемника выполнен на четырех D-триггерах типа Защелка и осуществляет по сигналу EWR Разрешение записи прием и хранение информации, поступающей по двунаправленной шине В. При низком уровне сигнала EWR информация с выводов В передается на выходы DR, при высоко.м уровне сигнала EWR информация, поступившая на выводы В, запоминается на D-триггерах и хранится в течение всего времени, пока на вывозе EWR присутствует сигнал высокого уровня. Передача информации с тин D.\ и DB на шину Вис нтины В на шину DR происходит с инверсией. Микросхема КМ1804ВАЗ содержит схему генерации бита контроля четности. В зависимости от режима работы приемопередатч1н<а, определяемого состоянием входа ЕВ, схема генерации бита контроля четности передает на выход М2 сумму по mod 2 входных сигналов регистра передатчика (при ЕВ = 0) нли сумму по mod 2 выходных сигналов приемника (прн ЕВ=1), Назначение выводов КМ1804ВАЗ приведено в тябл. 3 со. ЛАОМЗ мо-т  Выходной Вуфер \дВВ Схепа генерации бита нонтропя четности Рис. 3,55. Структурная схема КМ1804ВАЗ

|