| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

Космонавтика Конструирование интегральных микросхем кого уровня на входе WR Запись или при поступлении сигнала управ тения записью с блока управления следующим адресом. Для некоторых микрокоманд регистр адреса может выполнять функцию счетчика, содг ржимое которого уменьшается на единицу по каждому положительному фронту тактового сигнала. При этом на входе WRдoлжнo быть установлено напряжение высокого уровня. Стек, состоящий из указателя стека, накопителя стека и схемы записи/считывания, предназначен для хранения адреса микрокоман ды и обеспечивает переход с возвратом при выполнении микропрограммы. Изменение указателя стека, представляющего собой реверсивный счетчик, и запись в один из пяти 12-разрядных регистров, со-ставлягощих накопитель стека, происходит по положительному фронт;, сигнала CLK. Управление работой стека осуществляется сигналами, вырабатываемыми блоко.\г управления следующим адресом. Указ;!-тель стека определяет регистр накопителя стека, содержащий инфор манию, записанную в стек последней. При записи в стек содержимое указателя стека увеличивается на 1, при считывании уменьшается ка 1. Схема позволяет осуществлять любую последовательность микроинструкций для обращения к стеку. При переходе указателя стека в состояние 5 на выходе FL Стек заполнен формируется низкий уровень напряжения. При записи в заполненный стек состояние указателя стека не изменяется, происходит запись в тот же регистр накопителя Стека, который определен ого указатетем. Счетчик микроко-манд, включающий регистр счетчика микрокоманд и схему приращения, предназначен для преобразования и хранения адреса, поступающего с выхода б тока выбора адреса Таблица 3.54

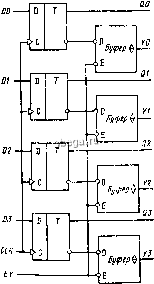

Управление счетчиком микрокоманд осуществляется сигналом CI, причем, если С1 = 0, адрес с блока выбора адреса передается немо-дпфицированным и по следующему сигналу CLK будет выполняться та же микрокоманда. Если С1=1, то в счетчике микрокоманд но положительному фронту сигнала на входе CLK запищется адрес, представляющий собой текущий выходной адрес, увеличенный иа 1. Назначение выводов КМ1804ВУ4 приведено в табл. 3.54. 3.7.6. Микросхема КМ1804ИР1 Микросхема КМ1804ИР1 представляет собой 4-разрядный регистр, предназначенный для записи и хранения информации. Структурная схема регистра представлена на рис. 3.50. Регистр состоит из четырех триггеров D-типа и четырех буферов, имеющих на выходе состояние Вык.1Ючено . Запись информации в регистр производится с информационных входов DO-D3 по положительному фронту тактового сигнала CLK. Информация, записанная в регистр, считывается либо с прямых выходов триггеров Q0-Q3, либо с выходов буферов Y0-Y3. Считывание с буферов осуществляется при наличии на входе EY Разрещение выходов Y напряжения низкого уровня. При напряжении высокого уровня па входе EY выходы YO-Y3 находятся в состоянии Вы:<лючено . Назначение выводов КМ1804ИР1 приведено в табл. 3.55.  pz в2 Рис. 3.50. Структурная схема КМ1804ИР1 Рис 3 5L Функциональная схема КМ180ШР1

3.7.7, Микросхема КМ1804ВР1 Микросхема КМ1804ВР1 представляет собой схему ускоренного переноса и позволяет организовать параллельные цепи перенос,! в процессоре разрядностпЮ до 20. Функциональная схема КМ1804ВР1 представлена на рис. 3.51. На микросхему поступают до четырех пар сигналов распространения и генерации переноса РО-РЗ. GO-G3 и сигнал входного переноса CI. Схема ускоренного перенос.i формирует выходные сигналы в соответствии со следующими уравнениями: Р = Р0 + Р1 +Р24-РЗ; С = P3G3 -f P2G2G3 + P1G1G2G3 + G0G1G2G3; СХ = C1G0+ POGO; CY = CIG0G1 -f POGOGl + PlGl; CZ = CIG0G1G2 + P0G0G1G2 + P1G1G2 + P2G2. Назначение выводов KM1804BPi приведено в табл. 3.56. Табл и ц а 3 . п

|