| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

Космонавтика Конструирование интегральных микросхем

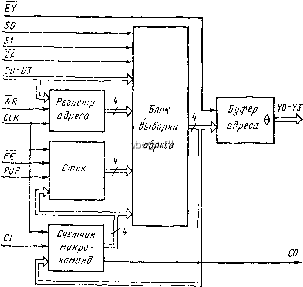

напряжения низкого уровня. Код микрокоманды задается снгиалачн MNSO-MNS8 на входе блока управления, который в соответстви.! с выполняемой микрокомандой формирует управляющие сигналы, поступающие на различные узлы мшросхемы. Назначение выводов КМ1804ВС2 приведено в табл. 3.50. 3.7.3. Микросхемы КМ1804ВУ1 и КЛМ804ВУ2 Микросхема КМ1804ВУ1 предназначена для формирования адреса .микрокоманды, подлежащей выполнению, н используется длч создания микропрограммных устройств упрйвлення. Структурная схема КМ1804ВУ1 представлена на рнс. 3.46. Рассмотрим назначетте основных узлов н принцип их взаимодействня. Блок выборки адреса формирует адрес управляющей памяти, где хранится микрокоманда, и представляет собой мультиплексор, на вход которого подается информация с различных источников: регистра адреса, стека, счетчика микрокоманд, шины данных DO-D3, маскирующей шины ORO-0R3. Управление выбором источника осуще-

R0-F3 Регистр адреса Стен Счетчии пикро-номанд Блок Выборки адреса fv 4 Буфер YO-YS Рис. 3.4С Сфукгурная схема 1\.М1804ВУ1 ствляется cHuia.iaMH SO, SI Выбор адреса . Кро.ме того, б.юк выборки адреса по CHiHa.iy ZA Нулевой адрес низкого уровня осуществляет переход к путевому адресу: формирует на выходах Y0-Y3 сигналы низкого ур:)вня независимо от состояния остальных входов. Адрес микрокоманды с блока в151боркп адреса через б>фер адреса, имеющий на выходе состояние Выключено , выдается па в.ы-ходную щину Y0-Y3. Перевод буфера адреса в состояние Вьпмю-чено осуществляется при иодаче на в:\од El Разрешение выходов Y наиря.кен.ия низкого уровня. Регистр адреса представляет собой 4-разрядный регистр, построенный на триггерах D-типа. Запись информации в ретистр адреса происходит по положительному фронту тактового сигнала CLK при наличии напряжения низкого уровня на входе WR Запись , Стек, состоящий из указателя стека, накоинтеля стека 4X4 и схемы записи/считывания, нредназиачен для хранения адреса микрокоманды и обеспечивает переход с возвратом при выполнении микропрограммы. Стек организован по принципу памяти магазинного типа и может работать в трех режимах в зависимости от состояния управляющих сигналов FE Разрешение стека и PUP Управление стеком : чтение без изменения состояния указателя стека; запись адреса микрокоманды с увеличением указателя стека на 1; выдача адреса Микрокоманды с уменьшением указателя стека на 1. Запись информации в стек производится из счетчика микро- команд по тактовому сигналу CLK. Счетчик микрокоманд выполнен в виде 4-разрядного рег}!стра и схемы приращения и предназначен для хранения и преобразования ннформацпи, поступающей с выхода блока выборки адреса. Управление счетчиком микрокоманд осуществляется сигналом CI Вход переноса . При установке на входе CI напряжения низкого уровня адрес с блока выборки адреса переда-ется немодифнцированным и по очередному сигналу CLK будет выполняться та же микрокоманда. При поступлении на вход CI напряжения высокого уровня в счетчик микрокоманд по положигельному фронту сигнала CLK будет записываться адрес, представляющий собой вь[ходной адрес микрокоманды, увеличенный на !. В микросхеме с помощ.-зЮ сигналов маскирования ORO-0R3 предусмотрена возможность модификации адреса на выходной шине Y. Подача напряжения высокого уровня на любой из входов OR0-ORS приводит к установке напряжения высокого уровня на соответствующем выходе. Назначение выводов КМ1804ВУ! приведено в табл. 3.51. Назначение микросхемы КМ1804ВУ2, состав ее основных узлов и принцип их взаимодействня в основном, те же, что и микросхемы КМ1804ВУ1. Структурная схема КМ1804ВУ2 представлена на рнс. 3.47. Отличие состоит в том, что в микросхеме КЛП804ВУ2 отсутствует маскирующая шина OR0-0R3 и входы регистра адреса объединены внутри микросхемы с информационными входами ir вы-  Рис, 3.47. Структурная схема КМ1804ВУ2

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||