| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

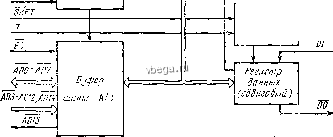

Космонавтика Конструирование интегральных микросхем мен пиформацией между ОЗУ и внешними устройствами в соответствии с ГОСТ 26765.51-86. Назначение выводов КР1801ВП1-030 приведено в табл. 3.33. 3,5.3. Микросхема КР1801ВП1-033 Микросхема КР1801ВП! 033 является многофункциональным устройством и может работать в режимах: интерфейса накопителя иа гибких магнитных дисках; контроллера интерфейса параллельного ввода/вывода; контроллера байтового параллельного интерфейса. Микросхема КР1801ВП1-033 совместно с микросхемой КР1801ВП!-034 может быть нспользоватта .т,ля организации 10- нлн 8-разрядного устройства параллельного ввода .вывода. Структурная схема КР1801ВП1-033 для режима интерфейса накопителя на гибких магнитных дисках (НГМД) иредставлена на рис. 3.29. Рассмотрим назначение основных узлов. Режим работы микросхемы задается иредварительно подачей на управляющие входы RCO-RC3 блока режима работы напряжения высокого уровня. Обмен информацией между процессором и контроллером НГМД осуществляется с помощью двух регистров: регистра команд и сос- RC0-RC5 режима раВоты 1NIJ SyfiC ввит WTBT Бпон синхрона -зациа Блок прерываний Но,чпарач1ор адресов Блок синхро- назаим Шда/вшдода  Регистр нопопд и сое/ваяний RPLY Рнс. 3.29. Структурная схема КР1801ВП1-033 в режи.ме интерфейса накопителя на гибких магнитных дисках тояннй п сдвигового регистра данных. Оба регистра 16-разрядиые, загружаются и считываются программно через буфер шины A,D Адрес/данные . Каждый из регистров имеет свой фиксированный адрес, предварительная установка которого осуществляется подачей на выводы RC4, RC5 определенного уровня напряжения. Компаратор адресов производит сравнение фиксированного адреса, заданного блоком режима работы, с адресом, подаваемым на буфер шины A/D, и при их совпадении разрешает обращение соответственно к регистру команд и состояний или к регистру данных. Регистр команд и состояний предназначен для записи и хранения команд и управляющих сигналов, определяющих порядок взаимодействия микросхемы с контроллером НГМД. Установка микросхемы в исходное состояние осуществляется сигналом INIT Установка , при этом микросхема вырабатывает сигнал SET Начальная установка , который используется для приведения механизма и электронной части НГМД в исходное состояние. Организация обмена информацией между системной магистралью и внутренней магистралью микросхемы производится блоком синхронизации в соответствии с ГОСТ 26765.51-86. Взаимодействие микросхемы с контроллером НГМД осуществляется следующим образом. По окончании выполнения текущей команды контроллер НГ.МД устанавливает сигнал DONE Завершено , который разрешает запись очередной команды в регистр команд и состояний. Наличие признака пуска в нулевом разряде команды формирует сигнал RUN Пуск , который, поступая на контроллер НГЛ1Д, инициирует прием команды. Контроллер снимает сигнал DONE и подает на вход SHFT Сдвиг данных серию из восьми импульсов. При этом происходит сброс сигнала RUN, а блок синхронизацип ввода,/вывода обеспечивает выдачу команды в последовательном коде на вывод DO Выход регистра данных . В зависимости от принятого кода команды контроллер НГМД устанавливает сигналы Т Направление передачи и TR Требование передачи . Сигнал Т указывает направление передачи байта информации. При наличии на входе Т напряжения низкого уровня информация передается от контроллера НГМД к микросхеме. Сигнал TR указывает, что контроллер готов принять/передать байт информации. Установка сигнала TR вновь вызывает формирование сигнала RUN и серию импульсов на входе SHFT: восемь для синхронизации адреса сетстора и дорожки, семь для с1шхрон1!зации данных, которые в зависимости от состояния сигната Т синхронизируют ввод информации через вход DI или вывод ее через выход DO. По окончании выполнения очередной команды тюнтроллер НГМД устанавливает сигнал DONE. При условии установки в регистре команд признака разрешения прерывания IE, появление сигнала DONE формирует сигнал VIRQ Требование прерывания . Выполнение процедуры прерывания стандартное Назначение выводов KPI80! ВП1-033 в режиме интерфейса НГ.МД приведено в табл. 3.34. Структурная схема КР1801ВП1-033 при работе в режиме контроллера интерфейса параллельного ввода/вывода представлена на рис. 3.30. Микросхема формирует управляющие сигналы, обеспечивающие прием информации из регистра-приемника и выдачу информации в регистр-источник. В качестве регистра-приемника н регистра-источника можно пспотьзовать микросхемы КР1801ВП1-034. Установка микросхемы КР 1801ВП1-033 в режим контроллера интерфейса параллельного ввода/вывода производится подачей определенных уровней напряжения на выводы RCO-RC3 Выбор режима . По- 14-300 209 lAKl RC0-RC3 Блок режит раВоты 1NIT SYNC DDUT WTBT Бпон синхронизации Бпон VIRQ WW Компаратор адресов Л1 да M0-AV7, AOIS Буфер АВв-ШТЩ шины Л/с Регистр состояний CSRO CSR1 RPLY

Рис. 3 30. Структурная схема КР1801ВП1-033 в режиме контроллера интерфейса параллельного ввода/вывода мимо выбора режпма работы микросхемы комбинации напряжений на выводах RCO-RC3 осуществляют нереадресацию регистров (состояния, источника и приемника) и векторов прерываний. Регистр состояний предназначен для записи и хранения команд и сигналов, обеспечивающих управление обменом инфор.мацией .меж ду внещними устройствами и системной магистралью. Нулевой и первый разряды регистра состояний соединены с внешними выводами CSRO, CSR1 и могут использоваться для имитации запросов прерн-ванпя в режиме автономной проверки. При ноступлении одного из сигналов REQA или REQB Требовз-ние А, В и при наличии в регистре состояний соответствующего разрешения нрерывг.ння lEA, 1ЕВ блок ирерываннй формирует сигна i VIRQ Требование прерывания . Выполнение процедуры прерыватигя стандартное. При одновременном ностутенни сигналов REQA я REQB более высокий приоритет имеет сигнал REQB. Блок управления вводом/выводом вырабатывает сигналы NDR, BIR и BOR при записи соответственно слова, старшего или младшего байга в регистр-источник и сигналы DTR и ORR при чтении wui-ветственно из регистра-приемника и регистра-источника. Для уве.г,!-чения длитеibHocTH сигналов DTR и NDR можно использовать RC-ue-почку, подключение которой к выводам RDO и RD1 показано на

|