| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

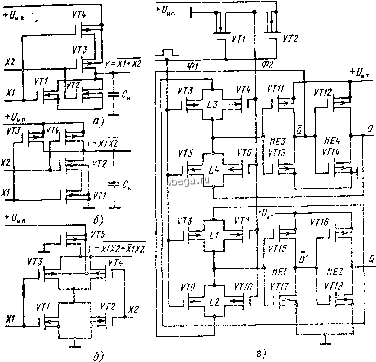

Космонавтика Конструирование интегральных микросхем TUt тиг- TUt . dIpCt ~zCt -и, Tufi Л-П-Л .С2 77/21 Л П Г1 Рис. 2.27, Схема двухтактного динамического регистра на р-канальных МОП-транзисторах иа п разрядов (а) и последовательность тактовых импульсов (б) Наибольшее распространение получили схемы двух,- трехфазных квазнсгатическнх триггеров П-тппа. Напомним, что триггеры, пазы-вае.мые также триггерами-защелками, представляют собой устройство с двумя устойчивыми состояниями и одним информационным входом. Квазистзтические D-триггеры часто используются для построения регистров. При этом цепи, управляющие записью и стви-гом, а также формирователи фаз входят в состав микросхем. Это обстоятельство позволяет использовать в квазистатпческих регистрах, являющихся многофазными системами, однотактный внешний сигнал, подобный однотактному сигналу Т! для двухфазного D-триггера. Недостатком квазистатических регистров является потребление мощности D-триггерами в режиме хранения иттформации. Поэтому более широкое распространение получили динамические регистры иа рМОП-траизисторах. Динамические двух- или четырехтактттыи регистры используются как регистры сдвига и обеспечивают необходимую задержку в схемах логических и арифметических узлов ЭВМ и устройств дискретной автоматики. Рассмотрим работу двухтакт ного динамического регистра на рМОП-транзисторах (рис. 2.27, а) [3]. Разряд регистра содержит два инвертора, собранных на трех транзисторах каждый (VTl-VT3 и VT4 -VT6). Тактовый импульс ТП1 поступает одновременно иа затвор нагрузочного транзистора VT1 первого инвертора и на затвор VT3. Тактовый и\гпульс ТИ2 поступает иа затвор нагрузочного транзистора VT5 н одновременно нт затвор VT6, Рассмотрим, 1:аким образом осутцсствляется запись информации и ее сдвиг. Пусть на вход первого младшего разряда регистра подан сигнал, соответствующий 1 . В результате паразитная емкость С1 заряжается и открывает транзистор VT2. При поступлении тактового импульса ТИ1 открываются транзисторы VTI и VT3 и паразитная емкость С2 разрялсается через открытый транзистор VT2. По окончании импульса ТИ1 на емкости С! сохраняется заряд, соответствующий О , в результате чего транзистор VT4 будет закрыт. Тактовый импульс ТИ2 откроет транзисторы VT5, VT6, поэтому будет образована цепь заряда паразитной входной емкости следующего разряда. Таким образом, за два тактовых импульса сигнал 1 , поданный на вход первого разряда, окажется переписанным на вход следующего разряда Последовательность тактовых импульсов приведена на рис. 2.27, б. Рассмотрим случай, когда входной сигнал соответствует уровню 0s>. Прн этом транзистор VT2 окажется закрытым и с приходом импульса ТИ! емкость С2 будет заряжена через цепь открытых транзисторов VT1, VT3, что обеспечит открывание транзистора VT4. С приходом импульса ТИ2 емкость CI второго разряда полностью разряжается через открытый транзистор VT4. В результате за время двух тактовых импульсов сигнал О , поданный на вход первого разряда, будет переписан на вход второго разряда. Так как тактовые импульсы поступают на все разряды регистра одновременно, то и процесс сдвига информации идет одновременно во всех разряда.х. Как видно нз схемы регистра, приведенной на рис. 2.30, а, потребление мощности в каждом разряде регистра происходит только в момент прихода тактовых импульсов, когда в каждом разряде открываются нагрузочные транзисторы VT1, VT5. Длительность тактовых импульсов определяется временем заряда паразитных емкостей С!, С2, ... и составляет 1...2мкс, что обеспечивает среднюю потребляемую мощность на разряд, в 3...5 раз меньшую, чем у ква-зистатичегких регистров На выходе динамического регистра д,-,?: получения хорошей нагрузочной способности включается .мощны,! выходной каскад (транзисторы VT и VT ), обеспечивающий быстрый разряд (через транзистор VT ) НЛП заряд (через транзистор VT) нагрузочной емкости Сн. Принцип работы четырехтактного динамического регистра аналогичен принципу работы двухтактного, но четырехтактные динамические регистры позволяют получить более высокую частоту работы схемы прн меньшей потребляемой мощности на разряд, 2.6.4. Принцип работы микросхем на КМОП-транзисторах Как видно из схемы инвертора, показанной иа рис. 2.26, s, она составлена из транзисторов разного типа проводимости (КМОП-тран-зисторов). Транзистор п-типа подключен riCTOKO.vi к нулевому потенциалу (общая шина), транзисгор р-типа - к положительной шине источника питания. Такая схема обеспечивает работу в режиме положительной логики, в котором работают наиболее широко применяемые серии К.МОП-схеч. Цифровые микросхемы на КМОП-транзисторах отличаются рядом преимуществ по сравнению с микросхемами на рЛЮП-транзи-сторах: они имеют малую мотиность потребления в статическом ре-нлше (единицы микроватт), относительно высокое быстродействие, хорошую помехоустойчивость и достаточно большую нагрузочну.ю способность [3]. Мощность, потребляемая схемой на КЮП-транзн-сторах, расходуется в основном во время переходного процесса на заряд выходных паразитных емкостей схемы и собственных емкостей транзистора. Поэтому с увеличением частоты переключения схемы,  Рис 2.28 Схемы на КМОП-транзпсторзх, о- ИЛИ-НЕ: б -и-НЕ; а - ИЛИ-И,ЛИ-НЕ; с -счетчый триггер а также вы-одиой эквиватснтиоп емкости погребляемая мощность возрастает, что моделируется уравнением Рд,ш = 2СнГри,п, где С,- эквивалентная емкость нагрузки; fp -рабочая частота; U n - напряжение источника питания. В статическом режиме мощность определяется напряжением питания и токами утечки закрытого МОП-транзистора. На КМОП-транзисторах, как и на рМОП-транзисторах, могут быть построены статические, квазистатические и динамические схемы. Статические логические схемы И -НЕ, ИЛИ -НЕ. ИЛИ - ИЛИ - НЕ и схема счетного триггера представлены на рис. 2 28 [1] Перезаряд емкости нагрузки С схем на КМОП-траизисторах всегда осуществляется через открытый транзистор р- или п-типа, что повышает быстродействие схемы. Для уменьшения мощности, потребляемой в динамическом режиме, необходимо снижать емкость нагрузки С . Минимальное напряжение питания схемы на КМОП-траизисторах определяется наирян{еиием огкрыпания Ьотк р р-ка-нального транзистора, так как оно больше, чем напряжение Uotk п

|