| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

Космонавтика Конструирование интегральных микросхем Таблица 23

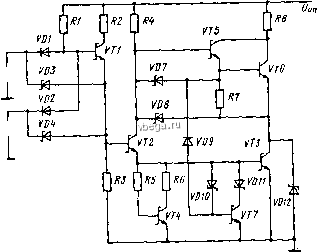

4 нс при мощности рассеивания 1 мВт на ЛЭ. Для оценки эффек-тивности цифровых микросхем и рабочих характеристик применяется показатель, равный произведению быстродействия в наносекундах на рассеиваемую мощность в милливаттах. Типовые рабочие характеристики различных модификаций ЛЭ И-НЕ серий SN54/SN74 и частота переключения триггеров приведены в табл. 2.3. Данные в табл. 2.3 приведены при Сн=15пФ и Rh=2kOm, Как видно из таблицы, микросхемы серий AS и ALS значительно улучшены по сравнению с остальными микросхемами серий ТТЛ и ТТЛШ. Схема AS обладает меньшей задержкой распространения и более высокой частотой переключения, чем любая схема других серий при незначительном увеличении мощности рассеивания. Стабильность параметров по постоянному току и времени переключения достигается во всем диапазоне температур. Серии микросхем AS и ALS совместимы между собой. Таким образом, можно сделать вывод, что серия AS 1530 является целесообразной заменой для высокоскоростных видов логических схем даже серии ЭСЛ, а серии ALS- 1533, КР1533 наиболее эффек-тивны в системах с низкими скоростями и могут конкурировать с микросхемами КМОП. Рассмотри.м более подробно технологию усовершенствованных маломощных схем с диодами Шотки (ALS). В отличие от технологии обычных маломощных микросхем с диодами Шотки (LS) технология схем ALS отличается применением ионной имплантации примесей вместо диффузии. Это дает возможное гь осуществлять точный контроль над глубиной легирования и разрешающей способностью. Отсюда более топкий эпитаксиальный слой и геометрия более малых размеров, снижающих паразитные емкости. Применение окисной изоляции между транзисторами вместо изоляции р-п-переходом также улучшает рабочие характеристики, уменьшая емкость коллектор-подложка. Рассмотрим инвертор серии 54ALS/74ALS, созданный на основе усовершенствованной схемы ТТЛ (рис, 2.11). Схема имеет следующие преимущества по сравне- :VD} Rif Л- VT5 R6 Vlk R7 VT7 livDit Рис. 2.И. Базовая схема инвертора усовершеиствоваиной маломощной серии с диодами Шотки типа ALS нию со схемами 54LS/74LS: полное ограничение диодом Шотки всех насыщающихся транзисторов, что способствует исключению накопления излищнего базового заряда и значительно уменьшает время выключения транзисторов; устранение излишнего накопления заряда, что позволяет получить более стабильное время переключения в диапазоне температур; обеспечение улучшения динамической помехоустойчивости при высоком логическом уровне за счет активного выключения выходного транзистора. Входной порог переключения устанавливается транзисторами при следующем соотношении: ипор=и ggyji+UE3VT3 + UE3YTb ~ d,3B. В схеме 54LS/74LS в отличие от приведенной выше отсутствует транзистор VT2. Когда открывается выходная схема Дарлингтона (см. рис. 2.11, транзисторы VT6, VT7), позволяющая осуществить формирование сигнала на выходе с сохранением низкого выходного сопротивления при высоком и низком логических уровнях, на выходе устанавливается напряжение высокого уровня Ugyx РИ выходном сопротивлении, равном 10 Ом. При небольших токах нагрузки схема Дарлингтона находится в ненасыщенном состоянии. При увеличении тока нагрузки она насыщается и выходное сопротивление возрастает до 58 Ом, определяясь в основном сопротивлением R7 = 50Om. Это сопротивление обеспечивает защиту каскада от короткого замыкания. Стабильность выходного напряжения высокого уровня осуществляется благо- даря активному выключению транзистора VT5 транзистором Vl4. Выходное напряжение определяется как -вых = -ип ~ (bvT6 3 + -бЭУТ6 + -бЭУТ? )  Рис 2,12. Базовая схема 2И-НЕ микросхемы FAST Выходное напряжение низкого уровня U°y устанавливается транзн-стором VT5, когда он включен. Этот транзистор включается цепью VT3, R3, когда на входе схемы высокий логический уровень, а транзистор VT2 включен. Коэффициент разветвления по выходу схемы равен 10 для микросхем серии 1533 и 20 для микросхем серии КР1533 при работе схем друг от друга. При этом гарантированный выходкой ток ];;, = 4мА. Наибольшим быстродействием среди схем ТТЛ обладают микросхемы серий 1531, КР1531 (функциональные аналоги 54F/74F). созданные на основе модернизнроваиного технологического процесса Isoplanaz II, позволяющего получать транзисторы с очень высокой, хорошо управляемой скоростью переключения и малыми паразитными емкостями. Частота переключепня у этих схем достигает 5 ГГц. Изо-планарная технология была разработана фирмой Fairchild и широко используется для производства биполярных ЗУ, микросхем КАЮП н ЭСЛ высокого быстродействия и ИЗЛ БИС. Изопланарная технология предусматривает изоляцию компонентов селективно выращенным слоем окисла в отличие от изоляции р-областя,ми, свойственной планарной технологии, н позволяет значительно сократить размеры компонентов и кристалла. Следует отметить, что из-за тонких слоев окисла п мелких диффузионных областей схемы типа FAST, как и указанные выше схемы ALS, AS. более чувствительны к повреждениям, вызванным электростатическими разрядами и требуют применения мер предосторожности. Запрещается размещать эти схемы на непроводящих пластмассовых поверхностях, в пластмассовой таре, необходимо заземлять оборудование и самих работников, занятых монтажом и испытанием микросхем. Рассмотрим (рис, 2.12) некоторые особенности логической

|

||||||||||||||||||||||||||