| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

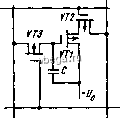

Космонавтика Конструирование интегральных микросхем Шииа считывания  Шииа Выборки Шииа столбца А Шииа столбца Б Числовая шияа 6) Рис. 4.4. Схема запоминающего элемента для динамических ЗУ: а - трехтранзисторная МОП-ячейка; б - одиотранзисторная МОП-ячейка саторе, образованном затвором МОП-транзистора VT1 и его подложкой. В данной ячейке VT2 - транзистор считывания, VT3 -записи. В начале цикла шины столбцов А и Б предварительно заряжены до некоторого отрицательного потенциала, близкого к Uo. При считывании информации из ячейки подается потенциал на щину считывания, в результате чего транзистор VT2 оказывается в проводящем состоянии. Если конденсатор С заряжен и напряжение на затворе транзистора VT1 превышает пороговое, то этот транзистор будет открыт и на шипу столбца Б попадет потенциал, близкий к Uo. Если же потенциал на затворе VT1 недостаточен для включения транзистора VT1, шина столбца Б остается в состоя1ШИ предварительного заряда с соответствующим отрицательным потенциалом. Из-за токов утечек заряд конденсатора С со Bpeiieiieii уменьшается. Время хранения заряда зависит от типа ячейки, технологии, изготовления, внешних условий и обычно составляет от единиц миллисекунд до нескольких секунд. Для восста1ГОвления, регенерации распадающейся информации, храни.мой в ячейке памяти, информационный код шины столбца инвертируется и вновь записывается в ту же ячейку. Это осуществляется с помощью усилителя регенерации, заряжающего шину столбца к, если шина Б сохраняет преднари-тслько занесенный в нее заряд. Если же разряжается шипа Б, то пре,дварнтсльно занесенный заряд сохраняется шиной А. Затем подается потенциал на шнну записи строки, и затвор транзистора VT1 приобретает потенциал, близкий к потенциалу шины А, благодаря че.му регенерируется код, хранимый в ячейке памяти. При записи на ишну столбца А подается нужный ннформациониын код, который н будет записан в виде заряда на конденсаторе С, Осиовны.м видом ячейки памяти для ДЗУ большой е.мкости (от 4 до 16Кбит и более) стал однотранзисторный ЗЭ, схема которого показана на рис. 4.4, б. Такая схема соответствует минимальному числу интегральных элементов, приходящемуся на бит хранимой информации. Одиотранзисторная ячейка памяти состоит из одтюго транзистора VT1, затвор которого соединен с шиной выборки строки и накапливающего конденсатора С. 1 УН - VT2 УТ6. УГ7 ! Рис 4.5. Схема запомш1аюш,С!о этемеита па КАОП-тр.и-.зиторах 4.2.3, Запоминающие элементы на КМОП-граязисторах При.менение КАЮП-трапзисюров потволяег существенно снизить мощность потребления и повысить быстродействие ЗУ. Схема ЗЭ матрицы ОЗУ иа КМОП-траизисторах приведена иа рис. 4.5. Адресация п запись информации производятся непосредственной подачей логических уровней по щинам Х,. Y. и D, D соответственно. Выбор ЗЭ осуществляется подачей по шинам X;, i, напряжения, со-от;тствующсго уровню <-: . При записи 1 в выбранный элемент И! шину D подается уровень О , а иа шину D - уровень Ь>. При Знисп *0;> иа щину Ri подается уровень 1 , а на шину D - уровень О , Считывание по напряжению пронзво,и1тся по шинам D и D, при эгом пиша считывания Сч соедтшяется с шиной общая . 4.2.4. Запоминающие элементы иа МНС11-трачзисторах Во всех рассмотренных микросхемах на биполярных и М.ОП-транзисторах для сохранения инфюрмации на ЗЭ обязательно наличие напряжения питания. При отключении н.апряжения питания информация теряется. Однако в ряде случаев откл.ючение питания необходимо, кролте того, возможность хранения информации при отключенном напряжении питания значительно снижает среднюю мощность, потребляемую ЗУ. Интегральная полупроводниковая структура - ,\\НОП-транзи-стор позволяет построить ЗУ. сохраняющее информацию при отключенном источнике питания В 1ШОП-траиз!1Сторах. в отлпчие от обычных МОП-структур, между гктенкой двуокиси крелыия и металлическим электродом затвор,-! помешается слон нитрида кремния. Накопление зарядов в области поверхности раздела слоев нитрида и двуокиси кремния дает возможность сохранять информацию при отключении источника питания в течение нескольких лет fl]. Слой двуокиси кремния предотвращает исренос зарядов в отсутствие на-пря/кения на затворе или когда оно ниже порогового значения. На рис. 4.6 показаны вольт-амперные характеристики (ВАХ) такого лЭ, npHiienfleMoro для построения матриц ПЗУ. Для записи инфор.мацни в ЗЭ на основе МНОП-структуры на затвор подается 20-300 30 -20 Рис 4 6 Вольт-амперная характеристика запоминак,щего элемента на МНОП-транзисто-рах напряжение соотвстсгвующего знака. Прн подаче определенно! о критического отрицательного напряжения на границе раздета слоев нитрида и двуокиси кремния возникает заряд, величина которого зависит от амплитуды, длительности импульса напряжения. При этом устанавливается состояние с высоким пороговым напряжением 6 ор в. При подаче также некоторого критического положительного напряжения на границе раздела возникает заряд, который снижает пороговое напряжение до величины Unop н. Разность UnopB-UnopH = AUnop называется межпороговой зоной [11. На вольт-амнерной характеристике, приведенной на рнс. 4.6, показаны высокое Lnop в и низкое Unop в пороговые иапряжени.я, соответствующие уровням 1 и 0->; нереключеиие схемы на МНОП-транзисторах из состояния 1 и О обеспечивается при изменении напряжения иа затворе от из = -28 В. до из=-г28В. Наличие межнороговой зоны AUnop=!2B позволяет отличать два состояния ЗЭ. Для считывания записанной информации ( 1 или О ) на затвор МНОП-транзистора необходимо подать напряжение считывания Uc4, удовлетворяющее условию Uuop ,i< <Uc,<UoopB. Таким образом, если подать Uc =-3,..-5 В, то ЗЭ, в котором была предварительно записана 1 (Unop е= 15 В) перейдет в состояние проводимости. Если же ранее был занисан О (UnopH = 3B), нри подаче напряжения считывания ЗЭ остается закрытым. Сигнал считывания определяется падением напряжения на нагрузочном резисторе iaлoгo номинала, включенном между выходом ЗЭ и шиной общей (в ПЗУ с двухкоординатной выборкой), или наличием тока в выходной цепи (в ПЗУ с пословной выборкой). Записанная в ЗЭ на .\ШОП-структуре информация сохраняется при отключенном напряжении питания длительное время, хотя в па-чале срока хранения несколько уменьшается межпороговая зона. Накопительные свойства МНОП-структур ухудшаются прн многократном повторении цикла считывание, запись, что обусловливает стремление использовать их для создания ПЗУ. Примером такого ПЗУ могут служить микросхемы КР1601РР1. Позволяют сохранять информацию при отключенном напряженин пита1И1я и микросхемы, Бияол:.е!Щые иа основе ларинной 1шжскиии заряда (ЛИЗ.ЮП). 4-3. Типы запоминающих устройств Микросхема ЗУ, как правило, поедставляет собой функционально законченное изделие, что позволяет создавать устрокства памяти с большой информаиионной емкостью непосредственным наращиванием разрядности и числа слов, Полупроводкиковые ЗУ по режиму занесения информации делятся на оперативные и постоян)1Ые; по режиму работы - на статические и дина>,!Ические; по принципу выборки информации - на устройства с произвольной и последователь-

|