| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

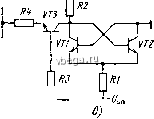

Космонавтика Конструирование интегральных микросхем ЗЭ22 Рис, 4.1. Структурная схема матрицы с пословной выборкой и одной ступенью дешифрации (а) и двухкоординатной матрицы с двумя ступенями дешифрации (б) нон шиной А потенциал которой в установившемся состоянии должен быть самым низким в схеме. Э\!иттеры 2 транзисторов VT1 и VT2 соответственно присоединяются к разрядным шина.м Р, и Р,. На разрядную шину Р, подается опорное напряжение Uon, общее для всех ЗЭ матрицы. На шину Pj подается напряжение Up. Соотношение мел<ду нааряжения.мн Ucn, Up и U, подав?емым в адресг1ую шииу. определяет режим работы ЗЭ: хранение информации, ее запись или счшывание. Рассмотрим работу ЗЭ в каждом из трех режимов. Режим хранения информации соответствует соотношению Ua< <(Uon = Up). Схема находится в одном из устойчивых состояний, при котором открыт транзистор VT2 или VT1. Ток протекает по эмиттеру 1 открытого транзистора в зависимости от того, какая и,1-формация была предварительно записана: 1 или О . Эмиттеры 2 обопх транзисюров обесточены. Рассмотрим режим считывания. Пусть в RS-триггер была заси-сана 1 . Считаем, что при этом транзисгор VT2 открыт, а VT1 закрыт За 1 принимаем наличие тока в цепи эмиттера открытого транзистора. Чтобы передать эту информацию в разрядную шину Р, необходимо переключить цепь эмиттеров закрыть схему по эмиттерам 1 и открыть - по эмиттерам 2, оставив прежним состояине транзисторов тригера (VT2 открыт, Vfl закрыт). Для этого необходимо сделать напряжение на адресной шине таким, чтобы выполнялось соотношение U,i> (Up=Uon). В эгом случае ток через эмиттер 2 открытого транзистора VT2 потечет в разрядную шину Pj. Наличие тока в разрядной шине < оответствует считываемой 1 , отсутствие (при закрытом транзисторе VT2 и открытом VT1) определяет считывание О . Условия режима записи гавнсят от состояния, в которое необходимо установить ЗЭ. Если триггер находился в состоянии 1 (транзистор VT2 был открыт, VT1 - закрыт), для заниси О необходимо по разрядной шине Pj подать потенциал Up>Uon, сохраняя соотношение Ua>Up. При этом триггер перейдет в новое состояние: тран- Разрядная *uni  Адресная т 5/7. Ъ£Г Рис. 4.2. Схема запоминающего элемента на двух инверторах ТТЛ (а) и временньге диаграммы его работы (б); схема запоминающего на двух инверторах НЛ элемента (а) зистор VT2 закроется, а VT1 - откроется. Для записи в ЗЭ 1 на шину Pj следует подать потенциал Up<Uon и обеспечить соотношение 1]а>1]оп. Временные диаграммы работы такого ЗЭ показаны на рис. 4.2, б Таким образом, у подобных ЗЭ иа биполярных транзисторах главными параметрами являются ток считывания 1сч и напряжение записи Up. Время выборки данных из ЗУ небольшой емкости на биполярных схемах ТТЛ может составлять 30...40 не. Ва.жнын параметр ЗУ - потребляемая мощность, она может составлять 0,5...1,5 мВт/бит, В последние годы разработаны ОЗУ на транзисторных структурах ИЛ, позволяющих снизить потребляемую мощность до 0,1 IBт/бит при времени выборки 150 нс. Принципиальная схема ЗЭ на И-Л приведена иа рис. 4.2, в. 4.2.2. Запоминающие элементы на МОП-транзисторах В зав1!симости от тина ЗЭ на основе МОП-транзисторов могут быть построены статические или динамические ЗУ. В первом случае в качестве ЗЭ служит статический триггер па р-канальных .МОП-транзисторах, а во втором - инфор.мация запоминается на емкость* затвора МОП-транзисторл. ЗУ на МОП-траизисторах, так же как и ЗУ на биполярных транзисторах, могут быть с пословной и двух-координатной произвольной выборкой. Пример простейшей схемы ЗЭ триггера для ЗУ с пословной выборкой приведен на рис. 4.3, а [1]. Триггер образован транз11сторами YT1-VT4. Управление триггером для записи и считывания осушест- £4-

Запас/, Запись Очитыбамие 1 О инфорпацтс Рис. 4.3. Схема запоминающего элемента для ЗУ с пословной выборкой {а) и временные диаграммы его работы {6) вляется переключением транзисторов VT5 и VT6. Временньш диаграммы работы такого ЗЭ представлены на рис. 4.3, б. В исходно.м состоянии напряжение па обеих разрядных щииах Upi и Uo разно нулю, а на щине слова А потенциал равен напряжению питания схемы. При этом транзисторы VT5 и VT6 закрыты, так как разность потенциалов между затворами и истоками по абсолютной величине меньше порогового напряжения. Триггер находится в одном из устойчивых состояний. Пусть, например, транзистор VT3 открыт, а VT1 закрыт. При записи 1 в щину слова подается отрицательный сигнал, изменяющий напряжение в ней до нуля, одновременно в разрядную тиипу Р подается положительный сигнал, изменяющий напряжение в ней до напряжения питания U n- При это.м транзистор VT5 открывается, так как разность потенциалов между затвором и истоком становится отрицательной. Положительный сигнал поступает на сток VT1 и на затвор VT3. Разность потенциалов между затвором и истоком VT3 становится меньше порогового напряжения, и транзистор закрывается. После закрывания VT3 открывается транзистор VT1 и иа его стоке устанавливается положительное напряжение, что соответствует состоянию 1 . Напряжение на стоке VT3 становится равным нулю. Для записи О в ЗЭ необходимо при нулевом напряжении на шине слова подать напряжение U в разрядную шину Р°. При это.м через открытый транзистор VT6 положительное напряжение, попадая на затвор транзистора VT1, закрывает его, что приводит к закрыванию VT3. Для считывания информации, предварительно записанной в ЗЭ, необходимо подать отрицательный сигнал только на шиьу слова, изменив в ней наиряжение до нуля. При этом транзисторы VT5 и VT6 оказываются открытыми и через транзистор, присоединенный к точке ipnrrepa с положительным поте1щиалом, протекает ток, поступающий в соответствующую разрядиу.ю шину и далее на усилитель считывания. Схемы запоминающих элементов динамического ЗУ на Р-канальных МОП-транзисторах представлены на рис. 4.4 fl]. Разрабога1ы два варианта ЗЭ для динамических ЗУ: на трех и oaIiO.m транзисторе. Их схе.мы предсгавлеиы на рис. 4.4. В трехтранзпсторьой ячейке памяти (рис. 4.4, а) информация хранится в виде заряда иа коиден-

|

|||||||||||||||