| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

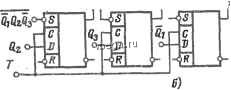

Космонавтика Электроизоляционные конструкции и изоляторы сигнала С осуществляется установка триггеров в состояния, обусловленные сигналами на R- и S-входах. Операция сдвига служит основой умножения двоичных чисеЛ; например, сдвинув число 1 О 1 влево на один разряд, увеличим его вдвое (10 10). Сдвиговый регистр с последовательным вводом информации Рис. 15-46. Регистр-память. пределитсчь на три канала имеет три состояния, в каждом из которых на одном из выходов имеется логическая единица, а на остальных выходах - нуль. Последовательность состояний распределителя можно записать кодовыми словами: 100, 010, 001... Можно выполнить распределитель с иной продолжительностью действия логического сигнала на выходах. Например, в схеме с состояниями выхода 011, 101, ПО логическая единица присутствует на каждом из выходов в течение двух тактов. В схемном отношении распределитель не является специфическим классом схем; функцию распределения сигналов по нескольким каналам на выходе можно реализовать на основе известных схем счетчиков и регистров. Число состояний счетчика или регистра определяется необходимым числом независимых выходных каналов. Выходы счетчика (регистра) связаны с выходными каналами распределителя через дешифратор. В счетчике Л=3 (рис. 15-45) состояния чередуются в последовательности: 00, 10, 11..., состояние 01 запрещено. Дешифратор с выходами а, Ь, с должен реализовать функции: a=Qi, b=QiQ2, c=Q2. 272 С Рис. 15-47. Регистр сдвига. показан на рис. 15-47. В момент поступления тактирующего импульса С в первый триггер запишется сигнал х, который действовал на входе Di. Второй импульс перепишет этот сигнал во второй триггер и т. д. Таким образом, всегда Qi-hi.t+i = Qi,t, где Qi,t - выход i-ro триггера на такте t. Путем введения дополнительных управляемых связей между триггерами получают возможность сдвига записанного слова как вправо, так и влево. Некоторые виды регистров также выпускаются в виде интегральных схем с повышенной степенью ин- теграции (К1ИР201, К1ИР203, К1ИР205, К1ИР207, К1ИР204, 2ИР301, 2ИР302, 2ИР401, 2ИР402). Распределители Распределитель представляет собой разновидность схемы с памятью, которая распределяет входные сигналы по нескольким каналам на выходе. Очевидно, число независимых каналов не может быть больше числа состояний схемы. Простейший рас- Синтез схем с памятью Каждая схема с памятью представляет собой автомат, который характеризуется наборами входных и выходных сигналов и набором внутренних состояний. Наиболее простой из автоматов - двоичный счетчик - имеет единственный вход, регистр по рис. 15-46 имеет три входа и допускает 2=8 комбинаций входных сигналов. Для того чтобы синтезировать схему, необходимо выполнить определенную последовательность как формализуемых, так и неформализуемых операций. Рассмотрим их на примере синтеза схемы, которая при подаче на ее вход импульсов устанавливалась бы последовательно в шести циклически повторяющихся состояниях: ООО- 001-011-111-110-100-000. Выберем в качестве элементарных автоматов для синтеза этой схемы D-триггеры, функция возбуждения которых приведена выше. Переход схемы в каждое последующее состояние Zt+i обусловлен входным сигналом х и предыдущим состоянием zr. et+i = f(x, zt). Поскольку число состояний известно, можно определить минимально необходимое количество триггеров как ближайшее большее целое от логарифма N по основанию 2: m = gioga Щ\ в нашем случае т=3. Составим кодированную таблицу переходов (табл. 15-19), которая будет содержать шесть строк (по числу состояний автомата), а в столбцах запишем состояния Таблица 15-19

триггеров в двух смежных тактах: t и -f 1. Переход из состояния Qt в Qt+i происходит под действием входного сигнала. В правых  Рис. 15-48. Синтез автомата. а - последовательность состояний; б - принципиальная схема. столбцах записываются те значения входных сигналов для D-триггеров, которые осуществляют этот переход. Так, в первой строке записано, что под действием тактового сигнала схема должна перейти из состояния ООО в состояние 001, т. е. первый и второй триггеры должны перейти из состояния О в состояние О . На основании табл. 15-17 записывается необходимый для этого перехода входной сигнал £>i=£>2=0. Триггер 3 должен сменить состояние с О на 1. Для этого вход £з = 1. Объединяя функции возбуждения по столбцам, получаем, что на вход Dl должна быть подана логическая единица при наборах 011, 111 и 110 в такте t. Записывая эту функцию в канонической дизъюнктивной форме, получаем: Di = QiQQs V Q1Q2Q3 V q1q2q3 = = Q1Q2 V QaQs-Аналогично г>2 = QiQs V q2q3; Полученные выражения можно упростить, если учесть, что два состояния (010 и 101) отсутствуют в таблице, тогда из карты Карно (рис. 15-48, а) следует, что каждую тройку состояний можно объединить с одним из отсутствующих: Di = Q; D2=q3; Ds=Qi. Наконец, необходимо позаботиться о том, чтобы при появлении одной из запрещенных комбинаций (010 или 101) схема автоматически переходила в одно из рабочих состояний. Если на это рабочее состояние не накладывается никаких ограничений, то достаточно изменить состояние любого нз трех триггеров. Например, на рис. 15-48,6 на вход S первого триггера подается сигнал, который переводит схему из состояния 010 в состояние ПО, а состояние 101 также сделано неустойчивым: благодаря воздействию на установочный вход второго триггера получаем переход 101-111. Таким образом, можно сформулировать последовательность операции синтеза несложных автоматов: 1) определение множества состояний автомата; 2) определение минимального числа би-стабильных ячеек (триггеров); 3) кодирование состояний автомата, т. е. установление однозначного соответствия между каждым состоянием автомата и набором состояний триггеров; 4) составление кодированной таблицы переходов; 5) описание функций возбуждений триггеров логическими уравнениями и их минимизация с учетом избыточных наборов; 6) исключение запрещенных состояний; 7) составление принципиальной схемы. Интегральные микросхемы с большой степенью интеграции и микропроцессоры Надежность узлов, вынолненных на микросхемах, во многом определяется числом паяных соединений. Поэтому естественным желанием потребителей было получить такую интегральную схему, которая одна полностью выполняла бы поставленную задачу. В принципе такой путь возможен, но экономически он становится рентабельным лишь при больших партиях таких специализированных ИМС. Развитие микроэлектроники выявило следующие возможные пути повышения степени интеграции: 1) выполнение интегральных схем общего применения со средней степенью интеграции. К таким схемам относятся уже упоминавшиеся счетчики, регистры, а также комбинационные схемы: дешифраторы, сумматоры, мультиплексоры; 2) выполнение специализированных схем частного применения со средней степенью интеграции на основе гибридных ИМС; 3) выполнение интегральных схем с большой степенью интеграции, выполняющих функции процессоров - микропроцессоров. Разработка микропроцессоров стала возможной, когда появились монолитные ИМС со степенью интеграции до нескольких тысяч и десятков тысяч компонентов в одном кристалле. На таких ИМС выполняются узлы, составляющие основу ЭВМ; арифметико-логическое устройство, устройство уп- равления, устройство памяти и ввода-вывода информации. Универсальность микропроцессоров обусловлена возможностью выполнения самых различных программ, закладываемых в памяти. Таким образом, вместо аппаратурного пути решения разнообразных задач, как это делалось на основе ИМС общего применения путем построения специально разработанных схем, здесь реализован программный путь. Микро-ЭВМ может выполнять любые арифметические и логические операции, благодаря чему они применяются как для управления технологическими процессами, так и для решения вычислительных задач. . Список, литературы 1Б-1. Нефедов А. В., Гордеева В. И. Отечественные полупроводниковые приборы и их зарубежные аналоги. - М.: Энергия, 1978. - 208. 15-2. Агаханяи Т. М. Основы транзисторной электроники. - М.: Энергия, 1974. - 286 с. 15-3. Степаненко И. П. Основы теории транзисторов и транзисторных схем. - М,: Энергия, 1977. - 672 с. 15-4. Транзисторы и полупроводниковые диоды/Под ред. Н., Ф. Николаевского. - М.: Советское радио, 1963. - 647 с. 15-5. Виноградов Ю. В. Основы электронной и полупроводниковой техники. - М.: Энергия, 972. - 536 с. 15-6. ГОСТ 15133-77. Приборы полупроводниковые. Термины и определения. 15-7. ГОСТ 20003-74. Транзисторы биполярные. Электрические параметры. Термины, определения и буквенные обозначения. 15-8. ГОСТ 19095-73. Транзисторы полевые. Электрические параметры. Термины, определения и буквенные обозначения. 15-9. ГОСТ 20332-74. Тиристоры. Электрические параметры. Термины, определения и буквенные обозначения. 15-10. СТ СЭВ 1125-78. Приборы полупроводниковые силовые. Термины, определения и буквенные обозначения. 15-11. Справочник по элементам радиоэлектронных устройств/Под ред. В. Н. Дулииа, М. С. Жука. - М.: Энергия. 1978. - 576 с. 15-12. Справочник по интегральным микросхемам/Под ред. Б. В. Тарабрина. - М.: Энергия 1977. - 584 с. 15-13. Шалимова К. В. Физика полупроводников. - М.: Энергия, 1976.- 416 с. 15-14. ГОСТ 19480-74. Микросхемы интегральные. Электрические параметры. Термины, определения и буквенные обозначения. 15-15. ГОСТ 18683-73. Микросхемы интегральные логические. Методы измерения электрических параметров. 15-16. ГОСТ 19799-74. Микросхемы интегральные аналоговые. Методы измерения электрических параметров и определения характеристик. 15-17. Гутииков В. С. Применение операционных усилителей в измерительной технике. - Л.: Энергия, 1975. - 120 с. 15-18. ГОСТ 18421-73. Усилители операционные. Термины и определения. 15-19. Рутковски Дж. Интегральные операционные усилители. Справочное руководство. - М.: Мир, 1978. - 324 с. 15-20. Букреев И. Н., Мансуров Б. М., Горячев В. И. Микроэлектронные схемы цифровых устройств. - М.: Советское радио, 1975. - 368 с. 15-21. Будинский Я. Логические цепи в цифровой технике.- М.: Связь, 1977.-392 с. 15-22. Вальков В. М., Ильюшенко Ю. М. Цифровые интегральные схемы, микропроцессоры и микро-ЭВМ. - М.: Советское радио. 1977. - 104 с.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||