| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

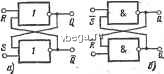

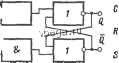

Космонавтика Электроизоляционные конструкции и изоляторы Реализация функций И и ИЛИ иа элементах И-НЕ, ИЛИ-НЕ показана на рис. 15-40. а,г. Возможность реализовать функции И, ИЛИ, НЕ делает набор полным. Это создает определенные удобства при проектировании, поскольку номенклатура элементов сводится к минимуму. Однако для реализации функциональных зависимостей на входы подаются всевозможные наборы аргументов, каждому набору соответствуют сигналы О (или 1) на одном выходе и 1 (или 0) - на остальных. Пример дешифратора на три независимых входа х, у, г приведен на рис. 15-41 (инверсные входные сигналы X, у, Z легко получить с помощью схем НЕ). Набору ООО соответствует сигнал О на выхо- & И1> е) г) Рис. 15-40. Реализация основных логических функций на элементах И-НЕ, ИЛИ-НЕ. о, г - И; е, е - ИЛИ. базе И-НЕ либо ИЛИ-НЕ необходимо записать выражения в форме, которая соответствует выбранной базе. Для базы И-НЕ выражения примеров 1 и 2 приведем к виду (рис. 15-38,6, 15-39,6) ii=ob\l ЬсУ ас=== аЬуЬсУ ас = = аЬ be ас; fl=:ab\/ bed = аЬ-bed. Для базы ИЛИ-НЕ соответственно (рис. 15-38, е и 15-39, е) fi={ayb)(by с)(ау с) = == а\/Ь V ЬУс V Vc; и=аЬ\/ bcd=a\/ Ь\/ by сУ d. Минимизация аппаратурных затрат практически не формализуется т. е. ее не удается свести к последовательности применяемых правил, однако для сравнения различных решений существуют методы, сводящиеся к оценке общего числа входов микросхем. Построение логической схемы сводится к последовательности действий: 1) составить таблицу соответствия; 2) описать логическую функцию на карте Карно или аналитически; 3) минимизировать логическое выражение, доопределив неполностью определенную функцию; 4) записать логическое, выражение в форме, соответствующей выбранному элементному базису; 5) составить принципиальную схему. Дешифраторы Раснространенный класс логических схем - дешифраторы. Дешифратор имеет т независимых IT}- T]-< XX уу ZZ входов и 2 выходов. На Рис. 15-41. Дешифратор на элементах И-НЕ. де О, на остальных выходах имеем логическую 1; набору 101 = 5 соответствует сигнал О на выходе 5 и т. д. Триггеры и триггерные устройства Рассмотренные выше логические схемы называют комбинационными, поскольку выходной сигнал однозначно определяется набором (комбинацией) аргументов на входах независимо от того, какие значения нринимали аргументы в предшествовавшие моменты времени. Между тем на практике часто возникает необходимость поставить логическую величину на выходе схемы в некоторую зависимость от предыстории. Покажем два примера задач такого рода. 1. Логический сигнал на выходе схемы должен принять значение 1, если входной сигнал у постунил не позже чем через 1 с после поступления сигнала х. Здесь накладываются ограничения на протяженность временных интервалов. Построение таких схем требует применения задержек, которые в зависимости от значения сигнала и требуемой точности выполняются либо на онерационных усилителях, либо, на логических элементах. 2. Логический сигнал на выходе схемы должен принять значение 1, если сигналы X, у, Z поступают на вход схемы в заданной последовательности. Здесь накладываются ограничения на последовательность изменения состояний, для чего их приходится запоминать. Число предшествующих состояний, которое необходимо запомнить для нормального функционирования схемы, определяет требуемую глубину памяти.  Рис. 15-42. Триггер RS. о -на элементах ИЛИ-НЕ; б - на элементах И-НЕ. Дальнейшее рассмотрение будет посвящено только схемам с памятью. Простейшим элементом памяти является iJS-триггер (рис. 15-42) (от анг. слов set - установка, reset - сброс). Он представляет собой схему с обратной связью, выполненную на элементах И-ЛЕ либо ИЛИ - НЕ. При системе обозначений рис. 15-42 функционирование обеих схем описывается одинаково. Qt+i - состояние выхода после поступления указанного набора входных сигналов. Из табл. 15-13 следует, что при i?=S=0 схема сохраняет свое предшествующее состояние, комбинации сигналов 01 и 1 О устанавливают выход в одно из состояний; 1 или О, и это состояние хранится (запоминается) после перехода к входной комбинации 0 0. Комбинация 1 1 считается запрещенной, поскольку действие обратных связей при этом нарушается и последующее состояние схемы не определено. Заметим, что для схемы рис. 15-42, б все входные сигналы в таблице следует инвертировать. Таблица 15-13 дополнительный вход С (от английского clock - часы), сигналы которого разрешают изменение состояния. Схемная реализация и диаграммы работы тактируемого RSi-триггера приведены на рис. 15-43. В интегральном исполнении выпускают-.ся тактируемые триггеры D- и JK-типов. Их функционирование описывается таблицами соответствия, логическими формулами и функциями возбуждения (табл. 15-15- 15-18). .5 -  ческими зависимостями и функциями возбуждения (табл. 15-14). Функция возбуждения показывает, какая совокупность сигналов на входах обеспечивает переход из состояния Qt в состояние Qt+i. Буквой b обозначено безразличное состояние входа. Различают асинхронные и синхронные (тактируемые) триггеры. Первые изменяют свое состояние только под действием входных сигналов. Тактируемые триггеры имеют 32* а] В) Рис. 15-43. Синхронный RS-триггер. а - схема; б - диаграммы работы. Таблица 15-14

Таблица 15-17

Таблица 15-18

двоичного счетчика где т - число триггеров. Аналогично выполняется счетчик на JK-триггерах. Если вход следующего триггера будет соединен не с инверсным, а с прямым выходом предыдущего, то получим счетчик на вычитание, число в котором бу- Счетчики Счетчиками называют схемы, которые могут находиться в N различных состояниях и переходят из одного состояния в другое в определенной последовательности

г-£ ПППППППП, п п п п Рис. 15-44. Двоичный счетчик иа сложение. а - схема; б - диаграмма состояний. под действием входного сигнала. Простейший счетчик на сложение (рис. 15-44) может быть построен на триггерах D- или JK-типов. Входной сигнал Т поступает на вход С первого триггера. Если соединить инверсный выход с входом D, то 3 соответствии с уравнением Qt+i=CDt=:CQt с приходом каждого импульса на вход С состояние выхода будет изменяться на противоположное. Момент изменения состояния совпадает с положительным перепадом сигнала С. Соединив инверсный выход первого триггера со входом второго, получим, что будет изменяться при положительных перепадах Qi, которые совпадают во времени с отрицательными перепадами Q\. Для установки всех триггеров в исходное (нулевое) состояние используют общий сигнал, подаваемый на все установочные входы R. После прихода очередного импульса на выходах Qs, Q2, Qi будем получать последовательность двоичных чисел 0 0 1, 010, 0 11..., соответствующих числу поступивших импульсов. Число состояний 1-]Кг j-- в, п п П Г Рис. 15-45. Счетчик иа 3. дет уменьшаться на единицу с приходом каждого счетного импульса. Можно выполнить управляемую систему связей между триггерами, которая позволяет изменять режим работы (сложение - вычитание). Такие счетчики называют реверсивными. Число состояний счетчика можно уменьшать, запрещая некоторые (избыточные) состояния. Так, для построения счетчика с тремя состояниями (JV=3) необходимо запретить одно избыточное состояние в схеме на двух триггерах (рис 15-45, а). Если в исходном состоянии Qi=Q2=0, то первый импульс изменит состояние первого триггера, поскольку /Ci=Q2=0. Второй импульс, не изменяя состояния первого триггера, у которого по-прежнему Ki=0, установит ч=\, поскольку У2=/?2=1. Наконец, третий импульс возвратит оба триггера в исходное состояние (рис. 15-45, б). Опрокидывание триггеров происходит в момент отрицательного перепада сигнала С. Для получения ЛГ=10 (десятичный счетчик) запрещают шесть избыточных состояний 3 схеме на четырех Триггерах. Четырехразрядные счетчики и счетчики на 10 выпускаются в настоящее время в интегральном исполиении как одна микросхема с повышенной степенью интеграции (К1ИЕ551. 2ИЕ301, 2ИЕ302, 2ИЕ303, 2ИЕ311). --. * Регистры Регистром называют устройство для-приема, хранения (запоминания), поразрядного логического сложения и сдвига инфор--мации. Входную информацию можно вводить в регистр одновременно во все разряды (параллельные регистры) или последовательно. Функция приема и хранения параллельной информации поясняется рис. 15-46. Входной набор (входное слово xj/z поступает на входы верхних схем И, а инвертированное слово - на входы нижних схем. И. Таким образом, на схемах И, связйнных с любым из триггеров, всегда будут взаимно . инверсные сигналы. В момент поступления .

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||