| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

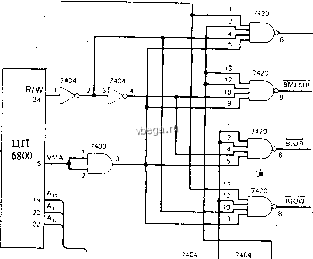

Космонавтика Архитектура 3-х шинных систем Схемы генерирования сигналов управления системы 6800 Сигналы управления системы Схемы дешифрирования управляющего сигнала ввод-вывод/память ф2(Л0 от тактового генератора 2- Схема геиерироваиня с помощью схем дешифрировании сигиа-ofij?j.j f * * на базе микропроцессора 6800. Наличие этой схемы обусловлено архитектурой ввода-вывода 6800 по аналогии с обращением к памяти. ?2(TTL) BMEMW ,  gvg с; л g 5 30 31 32 33 34 35 36 37 38 39 40 Z 80 1 Микропроцессор 14 15 12 8 7 9 10 . 13 22 21 20 19

Ю/М (0400-D7fF) Область памяти для ввода-вывода Рис. 2.31. Полная схема реализации Шины управления светена на базе микропроцессора 6800 с помощью схем дискретной логики, построенная на основе блок-схемы рис 2.30. ;MREQ Зг\ 4 74L3367

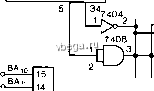

1,15 74LS367

7404 1,15 74LS245 В Do Направле , ние передачи 1 = - 0= - 74DD BMEMR 4>п BMEMW BIOR BIOW Рис. 2.32а. Схема шин: адреснс, данных и управления для михропроцессо* ра Z80. 9 10 11 12 13 14 15 16 17 18 19 20 6800 Микропроцессор 22 23 24 25 33 32 31 30 29 28 27 26 VMA R/W 74LS367

74LS367 BA10 BA .- Jl, 15 r74LS367

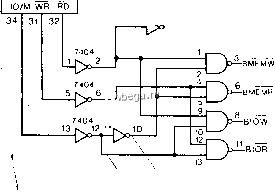

BA,. BA,3 BA,4 BA15 1,15 74LS245 BDo 8 BDi 6 BDa  В Ay. 7404 7404 lO/M 74LS42 02 (TTL)- Направление передачи 7420 - 02(TTL) 7420 BMEMW BMEMW 7420 7420 BIOR Blow Микропроцессор 8085 A,3 A,2 A Ain AD, ADe AD5 AD4 AD3 AD2 AD, ADo 28 27 74LS367 74LS04 BA,:

4> 74LS374 1 74LS374 7404 3 r- 4 1 74LS245 Направление передачи 7400

Рис. 2.326. Схема шин: адресной, данных и управления для микропроцессора 6800.-  !вслучае обращения к памяти 1 в случае запроса на ввод-вывод Рис. 2.32в. Схема шин: адресной, данных и управления для микропроцессора 8085. 8080 Микропроцессор Ао А, Аг Аз Ав-Лэ Ajo А А,2 А,3 А,4 Al6 Do D, Da D4 Ds Об O7 WR DBIN HLDA 741.S367 2 13 BAs If-Kl5 74LS367

BA = 13 BA, 31715 74LS367 2Г ВА,- BA,3 11,15

BMEMW BIOR Blow Эр я >> о STSTB . Строб состояния J. сГТИ Рис. 2.32г. Схема шин; адресной, данных и управления для микропроцессора 8080, . равления, как это показано на рис. 2.31. Для любого из рассмотренных выше микропроцессоров моно реализовать архитектуру ввода-вывода по аналогии с обращением к памяти. Однако для микропроцессора 6800 такая архитектура является обязательной. 2.20. Выводы Выше было показано, каким образом реализуется архитектура систем с 3 шинами на базе микропроцессоров 6800, Z80, 8085 и 8080. Управляющие сигналы микропроцессора использовались для генерирования сигналов шины управления и определения направления передачи информации по шине данных. При этом нет необходимости беспокоиться о синхронизации сигналов управления микропроцессора. Последний контролирует логические уровни и осуществляет синхронизацию сигналов, таких, как. RD, WR, DBIN и R/W. Из проведенного обсуждения ясно, что реализация архитектуры системы с 3 шинами для рассмотренных микропроцессоров-достаточно проста. Здесь не обсуждались такие детали, как подключение памяти к системе или генерирование тактовых импульсов. Эти вопросы вынесены в последующие главы. В заве)шение главы приведем полные схемы четырех рассмотренных микропроцессоров, имеющих архитектуру систем с 3 шинами. Эти схемы представлены на рис. 2.32а - 2.32г, где ясно видны три шины - адресная, данных и управления. Отметим сходство построения всех трех шин для указанных микропроцессоров. Необходимо подчеркнуть, что рассмотренная схема построения шины управления не является обязательной. Конкретная реализация этой шины в большой степени зависит от типа памяти и других ИС, используемых системе. Выбор представленной выше реализации шины управления сделан лишь с целью иллюстрации схожих сторон четырех рассматриваемых микропроцессоров. Однако приведенная техника построения шины управления может быть использована на практике и способствует пониманию архитектуры систем с 3 шинами.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||