| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

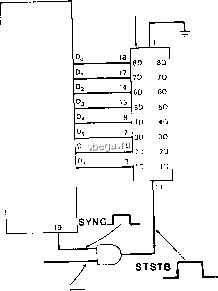

Космонавтика Архитектура 3-х шинных систем выше, что показано на рис. 2.25, где упомянутые сигналы управления обозначаются как MEMW, MEMR, I/OR, I/OW. Эти сигналы являются взаимно исключающими, а их активное состояние соответствует уровню логического 0. Таким образом, никакие два из них не могут быть одновременно в состоянии 0. При использовании микропроцессора 8080 в качестве контроллера системы устройство 8228 позволяет значительно упростить проектирование системы. Однако с целью оценки различ-иых альтернативных вариантов рассмотрим, каким образом четыре сигнала управления могут быть сгенерированы с помощью дискретных цифровых устройств. Это поможет лучше понять, как микропроцессор 8080 управляет техническими средствами системы. 2.1 S. Фиксатор состояния микропроцессора 8080 Центральный процессор 8080 генерирует на выводы шины данных байт информации, называемый словом состояния. Слово состояния генерируется для того, чтобы оповестить технические средства системы о намерениях микропроцессора в течение первого Т-цикла М-цикла. При переходе микропроцессора 8080 в состояние чтения данных из памяти вначале для индикации это-то состояния генерируется слово состояния. Это слово используется системой для установки правильного схемного соединения, используемого микропроцессором. При выдаче слова состояния на шину данных микропроцессор 8080 информирует об этом систему путем перевода в состояние логической 1 сигнала синхронизации на выводе № 19. Этот сигнал используется системой для формирования строба, пропускающего данные с шины данных в фиксатор, называемый фиксатором состояния, что показано на рис. 2.26. После фиксации слова состояния определенные биты информации состояния логически объединяются с сигналами DBIN и WR с целью формирования четырех сигналов шины управления. Схематически это показано на рис. 2.27. ~ Теперь шина управления системы в случае микропроцессора 8080 реализована с помощью схем цифровой логики. Необходимо подчеркнуть, что шина управления должна обеспечивать управление всех соединенных с нею входов. Поэтому необходимо буферирование шины управления. Для этого можно использовать контроллер 8228. Если шина управления построена с помощью цифровых логических cxei, как на рис. 2.27, то для ее буферирования можно использовать стандартное устройство 7400. > Подробнее см. Coffron J. W., Understanding and Troubleshooting the Microprocessor, Prentice-Hall, Englewood Cliffs, N. J., 1980. 74LS374 Микропроцессор 8080

Выходы фиксирог состояния L - значит фиксированный Строб-импульс от тактового r-i генератора -* Рис 2 26 Схема фиксации слова состояния с помощью схем дискретной логики Фиксация ова состояния устройством 74LS374 осуществляется по уровню 1 синхронизирующего импульса. ЦП 8080 18 3 MLS04 74. )4

Строб-импульс ISVNC og состояния от так-1-Jj-- I 74LS374 I-у inR состояния тового генератора Рис 2 27 Схема реализации шины управления системы на базе микропроцессора 8080 с помощью схем дискретной логики. Таблица 2.2 Таблица 2М Логаческке условии для выходов управляющих сигналов микропроцессора Z80 при указанных функциях системы

Сокращенное обозначение функций системы 2.16. Шина управления системы на базе Z80 Для управления в системе на базе микропроцессора Z80 используются сигналы, обозначаемые MREQ, IORQ, RD, WR. Логическая комбинация этих четырех сигналов позволяет реали- ЦП 20 >> 10 13 , Шнна управления системы для Z80 Рнс. 2.28. Полная схема реализации шнны управления системы на базе микропроцессора Z8o с помощью схем дискретной логики. зовать шину управления системы. Возможные логические комбинации указанных сигналов приведены в табл.- 2.2. Примерная реализация этих четырех сигналов управления показана схематически на рис. 2.28. 2.17. Шина управления системы нв базе 8085 Для построения шины управления микропроцессора 8085 нс-пользуем управляющие выводы, обозначаемые как Ю/М (вывод 34), RD (вывод 32) и WR (вывод 31). В табл. 2.3 приведены логические состояния сигналов на этих выводах соответственно функциям шины управления. Логические условия для выводов управляющих сигналов микропроцессора 8085 прн указанных функциях системы

Сокращенное обозначение функций системы Из табл. 2.3 видно, что при выполнении операций чтения или записи для устройства ввода-вывода (IOR и IOW) сигнал на выводе Ю/М (34) соответстйует состоянию логической 1, , 7400

7404 10= 1 в случае запроса на ввод-вывод 7400 ш с. МЕМ= 1 в случае обращения к паЫягн Рис. 2.29. Полная схема реализации шины управления системы на базе микропроцессора 8085 с помощью схем дискретной логики. При выполнении же операций чтения и записи в память (MEMR и MEMW) этот сигнал соответствует состоянию 0. Лри реализации функций, соответствующих обозначениям этих выводов (чтение и запись), на выводы RD и WR (32 и 31) подается сигнал 0. Таким образом, при выполнении чтения информации из памяти или с устройства ввода сигнал RD соответствует лбгическому 0. При выполнении же записи в памяп или на устройство вывода сигнал WR соответствует логическому 0. Логические схемы, необходимые для реализации управляющих сигналов в системе на базе микропроцессора 8085, приведены иа рис. 229. 2.18. Шина управления системы на базе 6800 Микропроцессоры 8080, 8085 и Z80 спроектированы таким образом, что выполнение функций доступа к памяти и к устройствам ввода-вывода осуществляется раздельно. Эти микропроцессоры имеют специальные команды, реализующие электрическую связь с памятью либо с устройствами ввода-вывода системы, что позволяет достаточно просто построить щину управления системы. Было принято, что во всех трех микропроцессорах-используется стандартная архитектура реализации операций: ввода-вывода. В микропроцессоре 6800 не существует специальных команд, устанавливающих электрическую связь либо с памятью, либо с устройствами ввода-вывода. Этот микропроцессор не различает память и устройства ввода-вывода; т. е. не различает тип схем, осуществляющих прием или генерирование данных. Все передачи в системе обрабатываются как обращения к памяти. Архитектура ввода-вывода подобного рода известна как ввод-вывод по аналогии с обращением к памяти. Для рассмотрения этой архитектуры введем специальный раздел с описанием адресного пространства памяти, используемого устройствами ввода-вывода. Адресное пространство микропроцессора 6800 включает 64К (2) адресов. Отведем часть из этих 64К адресов для использования устройствами ввода-вывода. При конкретном распределении ячеек памяти полезно пользоваться так называемой таблицей распределения памяти. С приобретением достаточного опыта в проектировании микропроцессорных систем распределение памяти осуществляется достаточно просто. Тем не менее и соображений методического характера для микропроцессора 6800 вопросы распределения памяти целесообразно рассмотреть детально. 2.19. Распределение памяти Распределением памяти называют разбиение имеющегося объема памяти в системе с целью реализации отдельных функций. Эта процедура характерна для любого микропроцессора. На распределение памяти влияет целый ряд факторов, некоторые из которых перечислены ниже: принятая архитектура ввода-вывода (линейная выборка, ввод-вывод по аналогии с обращением к памяти, стандартный ввод-вывод); используемые в Сис-. теме типы постоянных и оперативных запоминающих устройств-(ПЗУ и ОЗУ); частные особенности функционирования микро-, процессора. Подробно распределение памяти в системе будет рассмотрено на примере проектирования небольшой системы управляемой микропроцессором. Прежде всего обсудим некоторые особенности микропроцессора 6800 с целью обоснования конкретного распределения памяти. Вначале необходимо рассмотреть, каким образом микропроцессор начинает работу. С подачей питания микропроцессор переводится в рабочий режим с передачей управления в заранее определенную ячейку памяти, соответствующую адресу FFFE. Микропроцессор читает данные из ячеек FFFE и FFFF и формирует команду перехода по адресу, записанному в эти ячейки. После этого выполняется команда, расположенная по адресу перехода. Предположим для примера, что в ячейке FFFE записано число 08, а в ячейке FFFF -00. После считывания этих чисел управление передается в ячейку 0800 и начинается выполнение записанной там команды. Поскольку в описанной процедуре используются большие адреса, то область памяти, выделяемая для ввода-вывода, не должна располагаться в верхней части памяти. Отведем область памяти с адресами от 0400 до 07FF для использования в качестве адресов ввода-вывода. При этом возникает необходимость в распознавании этого адресного пространства и генерировании соответствующего сигнала (IO/M). Для формирования сигналов управления этот сигнал комбинируется с сигналом R/W микропроцессора. Описанная процедура показана на схеме рис. 2.30. На рис. 2.31 приведена полная схема реализации шины управления системы на базе микропроцессора 6800. Выбор адресного пространства 0400-07FF в качестве адресов ввода-вывода не является обязательным, а осуществлен лишь в иллюстративных целях. На рис. 2.31 показан также сигнал VMA, используемый для формирования шины управления системы. Этот сигнал генерируется микропроцессором и называется сигналом достоверности адреса памяти (Valid Memory Address). При выполнении команд на адресные линии может быть выдан несуществующий адрес. Если же сигнал VMA соответствует логической 1, то адрес, выданный микропроцессором, соответствует реально существующей ячейке ПЗУ или ОЗУ. Поэтому во избежание ложной записи в память системы необходимо использовать генерируемый микропроцессом сигнал VMA, уточняющий все сигналы на шине управления. Отметим также использование-при функционировании шины управления тактового сигнала фазы 2 (952). Из временных диаграмм микропроцессора 6800 можно заключить, что процессы в системе возбуждаются по заднему фронту импульса Ф2. Тем самым передача данных от микропроцессора в систему и наоборот начинается по заднему фронту импульса Ф2. Поэтому импульс Ф2 используется для формирования сигналов шины уп-

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||