| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

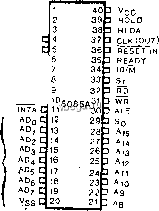

Космонавтика Архитектура 3-х шинных систем Xi С resetout С SOD SID TRAPC RST7.5 С R ST 6.5 С RST5.5 С intr с  Рис 2.14. Обозначения выводов для микропроцессора 8085. Отметим наличие выводов, обозначаемых ADo - AD?. Эти выводы относятся к шине данных с временным мультиплексированием, а также служат для передачи младшего байта адреса. С разрешения фирмы Intel.) вует логическому 0. Если информация на выводах 8085 ADo- ADr является адресной - Aq-А?, то ALE переводится в состояние 1. При переходе ALE из состояния 1 в состояния О информация на ADq-ADt должна быть зафиксирована. Это видно из временной диаграммы рис. 2.15. На рис. 2.16 показано, каким путем осуществляется фиксация данных техническими средствами применительно к полной информации 16-разрядной адресной шины для микропроцессора 8085. Отметим, что необходимость в использовании буферов с тремя состояниями 74LS367 возникает лишь для старших разрядов адреса Ag-А15, поскольку младшие разряды буфери-руются с помощью фиксатора 74LS374. Устройство 74LS374, выполненное в виде одной интегральной схемы, является одновременно фиксатором и буфером. Сигнал ALE на рис. 2.16 инвертируется за счет использования фиксатора с импульсным запуском. В соответствии со спецификациями 8085 адресные данные должны фиксироваться по заднему фронту сигнала ALE. С другой стороны, согласно спецификациям 8-разрядного фиксатора 74LS374, это устройство фиксирует данные по переднему фронту тактового импульса. Поэтому необходимо инвертировать сигнал ALE, поступающий от микропроцессора. Это позволит осуществить физически фиксирование информации ADq-AD7 в 8-разрядных фиксаторах 74LS374 по заднему фронту сигнала ALE. Фиксаторы другого типа, иногда используемые для выполнения этой функции, позволяют пропускать данные на выходы Q при состоянии, тактового импульса, соответствующем логической 1. При состоянии же О тактового импульса данные на выходе устройства сохраняются. Примером такого устройства является фиксатор 74LS373, пропускающий адресную информацию Ао-Ау по мере того, как она генерируется микропроцессо- Адрес доступен  Фиксация адреса Рис. 2.15. Временная диаграмма, определяющая взаимосвязь между сигна- Микропроцессор 22 8085

BD 8Q 7D 70 6D 6Q 5D 5Q 4D 4Q 3D 3Q 2D 20 ID 1Q

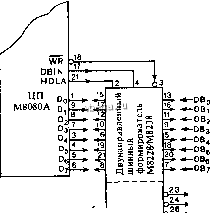

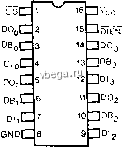

Буферированные адресные линии ром 8085. Различия во временных соотношениях для фиксаторов 74LS374 и 74LS373 показаны на рис. 2.17. Отметим, что для стробирования адресной информации от микропроцессора 8085 может быть использован любой фиксатор. Единственная предосторожность, которую необходимо со- ADo-AD Выход устройства 74LS374 Выход устройства 74LS373 Рис. 2.17. Временная диаграмма, определяющая взаимосвязь сигналов прн выдаче адреса, когда вместо устройства 74LS374 используется тор f4LS373. тает в режиме вывода, шина данных часто соединяется параллельно со многими входами. При этом Существует возможность того, что общая нагрузка от всех входов будет для шнны данных чрезмерной. Эта ситуация подобна той, которую мы обсуж- Разрешенное направление передачи ,- Буфер данных >--- Рнс. 2.18. о - однонаправленный буфер данных. В этом случае данные могут передаваться лншь в одном направлении; б - двунаправленный буфер данных. Данные передаются в обоих направлениях. Направление передачи определяется логическим состоянием сигнала управления передачей: в состоянии О данные проходят через буфер А, в состоянии 1 - через буфер В. Управление направлением передачи Запрешеиисе направление передачи данных Dp к микропроцессору В Do к системе блюдать при использовании фиксаторов разных типов, заключается в согласовании нагрузки по току для входов фиксатора и выводов ADp-AD? микропроцессора 8085 во избежание их перегрузки, т. е необходимо убедиться, что ток на входе используемого фиксатора не является слишком большим для микропроцессора 8085. 2.8. Пояснения к шине данных системы Как уже было показано, шина данных является двунаправленной. Это означает, что в некоторые промежутки времени информация вводится в микропроцессор (когда последний функционирует в режиме ввода), в другие же промежутки времени микропроцессор генерирует информацию и затем выводит ее в систему (работа в режиме вывода). Когда микропроцессор рабо- дали при рассмотрении нагрузки на адресную шнну. Для ее предотвращения вновь можно организовать буферирование. Однако для случая шины данных необходимо рассмотреть дополнительный фактор, а именно, то, что эта шнна данных в отличие от адресной шины не является однонаправленной. Она двунаправленная, и этот факт исключает возможность использования техники буферирования, применяемой в случае адресной шины. Рассмотрим рис. 2.18, а. Из рис. 2.18,0 видно, что рассмотренное выше буферирование может быть использовано лншь в том случае, когда информация по шине данных выдается в систему. Если же данные из системы будут передаваться в микропроцессор, они будут блокированы и не достигнут входов микропроцессора. На рис. 5.18,6 показана техника буферирования для двунаправленной шины, основанная на использовании логических схем с тремя состояниями. Отметим появление дополнительного сигаайа управления, логическое состояние которого задает направление буферированных данных. Например, при сигнале управления, соответствующем логической I, разрешается передача данных из системы к выводам микропроцессора. В случае же, когда состояние этого сигнала соответствует логическому О, разрешается передача данных от микропроцессора в систему через буфер А. Если один буфер с тремя состояниями открыт, другой в это время закрыт. Схема рис. 2.18,6 иллюстрирует общие принципы буферирования при двунаправленной передаче, которые могут быть использованы применительно к шине данных микропроцессора. Обсудим, каким образом описанная техника буферирования может быть реализована для четырех рассматриваемых микропроцессоров. Будем помнить, что буферирование при двунаправленной передаче требует сигнала управления для индикации направления передачи. Ниже будет показано генерирование этого сигнала для различных микропроцессоров. Таким образом, решение проблемы буферирования для двунаправленной шины показано на рис. 2.18,6. 2.9. Буферированная шина данных микропроцессора 8080 При использовании микропроцессора 8080 буферирование шины данных не вызывает беспокойства. Этот микропроцессор предназначен для использования совместно со специальной ин- Строб состояния (OTi228i  О Управление INTA ..MEMR Рис. 2.19. Схема соединения системного контроллера 8228 с микропроцессором 8080. (Устройство 8228 выполняет все функции буферирования шину данных и управления направлением передачи.) (С разрешения фирмы Intel.) тегральной схемой, называемой системный контроллер и шинный формирователь типа 8228>. Короче говоря, устройство 8228 осуществляет буферирование шины данных и автоматический контроль направления передачи данных. Поэтому применяя микропроцессор 8080, желательно использовать и устройство 8228. На рис. 2.19 показано КОНФИГУРАЦИЯ выводов ЛОГИЧЕСКАЯ СХЕМА УСТРОЙСТВА  dono- di,o- d0,o- НАИмЕНовлния выводов 002°

d0,°- -ODBo -ODB, -<DB2 -ODB3 DIEN -о- -ocS Рис. 2.20. Выводы и блок-схема устройства 8216. (С разрешения фирмы Intel.) совместное соединение устройств 8228 и 8080 при построении шины данных системы. Обсудим теперь, каким образом можно построить буферированную шину данных без использования устройства 8228. Это позволит лучше понять назначение различных сигналов управления в микропроцессорной системе на базе устройства 8080. Однако при использовании микропроцессора 8080 наиболее простым решением является применение системного контроллера и шинного формирователя 8228. Поэтому настоящее обсуждение вызвано лишь стремлением глубже разобраться в особенностях управления техническими средствами системы со стороны микропроцессора 8080. Двунаправленные буферы для шины данных оформлены в виде двух отдельных интегрйльных схем, именуемых устройст-

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||