| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

Космонавтика Архитектура 3-х шинных систем сти до определенного уровня и оставаться на этом высоком уровне вплоть до выработки сигнала подтверждения прерывания. Следующее прерывание на входе TRAP может быть зарегистрировано только тогда, когда уровень сигнала иа нем изменится от низкого до высокого уровня. Таким офазом устра- яются ложные срабатывания, которые могли бы возникнуть / из-за шумов или других помех. На рнс. П.5 представлена схема формирования запроса на прерывание TRAP, содержащаяся в микропроцессоре 8085А. Отметим, что во время обработки прерываний TRAP, RST 7.5, RST 6.5, RST 5.5, INTR, до тех пор пока не будет выполнена команда EI, запрещены все прерывания, кроме прерывания по входу TRAP. Прерывание TRAP является особым в том смысле, что оно запрещает прерывания, но не изменяет предыдущее состояние входа разрешения прерывания. Выполнение команды RIM после прерывания TRAP позволяет определить состояние маски прерываний независимо от того были ли разрешены или запрещены прерывания до наступления прерывания TRAP. Все последующие выполнения команды RIM дают текущее состояние маски прерываний. Выполнение команды RIM после прерываний по входам INTR, RST 5.5, RST 6.5 и RST 7.5 также будет информировать о текущем состоянии маски прерываний, обнаруживая, что прерывания заблокированы. Допустимые предельные значения (8085А/8085А-2) Температура окружающей среды О-70°С Температура устройства памяти -65--f- 150 °С Напряжения на всех выводах по -0,5--f-7В отношению к корпусу Мощность рассеяния 1,5 Вт Таблица 4 Характеристики по постоянному току (Если особо не оговаривается, то Та=0-70°С, Vcg=5 В±5%, Vss-О В.) OSotHaieHHe ViL VlH Vol VoH Icc ViLR ViHR Параметр Значение Низкое входное иапряжение Высокое входное напряжение Низкое выходное напряжение Высокое выходное на пряжение Ток источника питания Ток утечки на входе Ток утечкн на выходе Низкий уровень иа входе RESET Высокий уровень на входе -0,5 2,0 -0.5 2.4 4-0.8 VcH-0,5 0,45 ±10 ±10 -i-0.8 Vcc+0.5 Единица измерения Условия проверки в в в мкА мкЛ IoL=2 мА 1он=-400 мкА Vin=Vcc 0,45 VVotiTs <Voc чАР0-Р7 8085А Мкшмальиый комплект ESET lOUT TIMER оит,- TIMER IN \/0-7 lO/M 8156 (ОЗУ -)- yct-BoB/B-i: счетик/ таймер) Примечание: Допустимое соединение J It \Aio\/5- lit ihdy 8355 (ПЗУ -t- yct-bo B/B) или 8755A (ППЗУ -Ь уст-во В/В) Рис. П.6. Микропроцессорная система MCS-85TM. (Минимальный комплект. Связь с устройствами ввода-вывода реализована по аналогии с обращением к памяти.) trap rst7 rst6 rst5 intr inta addr/ sscc JdLi S08SA hlda sod reset sid out s, io/ia(cs) data addr (cs) Стандартное устройство памяти reset lo/M (cs) data Порт B/B. управление Стандартное уст-bo B/B ►vcc ► co cc Phg. П.7.Система MCS-85. (Используются стандартные устройства памятк.) Описание выводов ЦП Z80, Z80A > MREQ-ORQ- 5Р - WR RFSH- I NT -i NMI - RESET- Земля ЦП-280 ЦП-280А

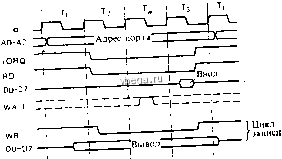

Рис. П.8. Назначение выводов микропроцессорон Z80, Z80A. Ао -Ai5 (адресная шина) Выходы с тремя устойчивыми состояниями. Активный уровень снгналон - высокий. Ao-Ai5 - выходы на 16-разрядную адресную шину. Адресная шина используется для передачи адреса памяти (может использоваться память объемом до 64 Кбайт) илн адреса устройства ввода-вывода. Do-Dr (шина данных) Входы-выходы с тремя устойчивыми состояниями. Активный уровень - высокий. К выводам Do-D? подключается восьмиразрядная двунаправленная шина данных. Шина данных используется для обмена данными между ЦП и памятью или между ЦП и устройствами ввода-вывода. Ml (машинный цикл) Выход. Активный сигнал - низкий. Сигнал Mi указывает, что в текущем машинном цикле проходит цикл выборки кода операции. MREQ (запрос памяти) Выход с тремя устойчивыми состояниями. Активный уровень сигнала - низкий. Сигнал запроса памяти указывает, что на адресной шине устанонлен адрес для выполнення операции записи или чтения памяти. 10RQ (запрос ввода/вывода) Выход с тремя устойчивыми состояниями.- Активный уровень сигнала - низкий. Сигнал IORQ указывает, что младший байт шниы адреса содержит адрес устройства ввода-вывода, который должен быть использован при выполнении операции ввода-нывода. Кроме того, сигнал IORQ генерируется после выдачи подтверждения прерывания. Тем самым указывается, что вектор прерывания может быть помещен иа шину данных. RD (чтение нз памяти) Выход стремя устойчивыми состояниями. Активный уровень сигнала - низкий. Сигнал RD указывает, что ЦП готов к чтению данных из памяти ил из устройства ввода. Адресованное устройство ввода или память должны использовать этот сигнал для стробирования при подаче данных на шину данных ЦП. WR (запись в память) Выход с тремя устойчивыми состояниями. Активный уровень сигнала - низкий. Сигнал WR указывает, что на шине данных ЦП содержатся данные, предназначенные для записи в память или для вывода на устройство вывода. RFSH (восстановление) Выход. Активный уровень - низкий. Сигнал RFSH указывает, что младшие 7 разрядов шины адреса содержат адрес восстановления для динамиче-ской памяти н текущий сигнал MREQ должен использоваться для выполнення восстановления днкамнческой памяти. HALT (останов) Выход. Активный уровень - пизкий. Сигнал HALT указывает, что ЦП Z80 выполнил команду HALT и ожидает появления либо немаскируемого, либо маскируемого прерывания, после наступления которого он продолжит функ-ционирование. Перед выполнением останова ЦП пересылает в память информацию, которая потребуется для возобновления его работы. WAIT (ожидание) Вход. Активный уровень - низкий. Сигнал WAIT указывает ЦП Z80, что адресуемая память или адресуемое устройство ввода-вывода не готовы для выполнення передачи данных. ЦП будет находиться в состоянии ожидания до тех пор, пока этот сигнал активен. INT (запрос на прерывание) Вход. Активный уровень - низкий. Сигнал запроса на прерывание генерируется устройствами ввода-вывода. Сигнал запроса на прерывание будет воспринят в конце выполнения текущей команды, если триггер разрешения прерываний (IFF), управляемый внутренними программными средствами, ус- тановлен в определенное состояние. NMI (немаскируемое прерывание) Вход. Активный уровень - низкий. Линия запроса на наскируемое прерывание. Это прерывание имеет более высокий приоритет по сравнению с прерыванием INT и всегда независимо от состояния триггера разрешения прерывания распознается в конце выполнення текущей команды. Сигнал NMI автоматически переводит ЦП Z80 к выполнению программы, команда которой имеет адрес 0066]б. RESET Вход. Активный уровень - низкий. Прн поступлении сигнала RESET выполняются следующие дейстиия: сброс триггера разрешения прерывания, очистка счетчика команд и регистров I и R. Во время установки начального состояния адресная шина и шипа данных переводятся в состояние высокого сопротивления, а дли всех управляющих выходных сигналов устанавливается неактивный уровень. BUSRQ (запрос шин) Вход. Активный уровень - низкий. Сигнал BUSRQ имеет более высокий приоритет, чем сигнал NMI, н всегда распознается в конце текущего машинного цикла. Он используется для перевода в состояние высокого сопротивления адресной шины, шины данных и тристайильных выходов сигналов управ- ления, после чего этими шинами могут управлять другие внешние устройства. BUSAK (подтверждение перевода шин в состояние высокого сопротивления) Выход. Активный уровень - низкий. Сигнал BUSAK подается на запрашивающее внешнее устройство для подтверждения того, что адресная шииа, шина данных и тристабильные линии шины данных перешли в состояние высокого сопротивления. Теперь внешнее устройство может управлять этими нами. Выборка команды Содержимое счетчика команд подается на адресную шину непосредственно в начале машинного цикла. Через половину периода следования тактовых импульсов подается сигнал MREQ. Задний фронт сигнала MREQ может быть использован для отпирания кристалла динамической памяти. Активное состояние сигнала RD показывает, что данные из памяти уже поступили на шину данных. ЦП выполняет выборку данных, когда проходит передний фронт синхронизирующего импульса, соответствующего состоянию Тз. Во время состояний Тз и Т4 цикла выборки производится регенерация динамической памяти, в то же самое время ЦП дешифрирует и выполняет команду. Сигнал управления восстановлением RFSH указывает, что восстановление возможности чтения динамической памяти завершено. Цикл М; JГЛ. А9-А15 ; MREQ RD WAIT Ml DO-D/ RFSH zj-t: -Адрес восста-, новления- f-\-j-Г Двод Рис. П.9. Врвменнйя диаграмма цикла М[. Цикл чтения из памяти и цикл записи в память Данная временная диаграмма циклов записи в память и чтения из памяти отличается от временнбй диаграммы цикла Mi, рассмотренной выше. Однако здесь, как и в цикле выборки, используются сигналы MREQ и RD. В цикла записи сигнал MREQ активизируется, когда уровни сигналов на адресной шине стабилизировались. Поэтому он может быть непосредственно использован в качестве сигнала отпирания кристалла динамической памяти. Линия подачи сигнала WR активизируется, когда данные на шине данных уже стабилизировались. Таким образом, этот сигнал можно непосредственно использовать в качестве импульса чтения-записи для любых типов полупроводниковой памяти. Приложение А0-А15 МНЕО D0-D7 . Адрес памяти WAIT :ti ij-L- r---T---4 Ввод Адрес нам Вывоп данных Рис П 10 Временная диаграмма цикла чтения из памяти и цикла записи г g память. Циклы операций ввода-вывода Рассмотрим временные диаграммы, соответствующие выполнению операции чтения данных из устройства ввода и операции записи данных в устройство вывода. Отметим, что во время выполнения операций ввода-вывода автоматически генерируется состояние ожидания, продолжающееся в течение времени Т*. Благодаря состоянию ожидания обеспечивается время, достаточное для дешифрирования адреса в порте ввода-вывода и для активизирования линии сигнала WAIT. 1 Цикл I чтения  Рис. П.П. Временная диаграмма цикла операции ввода и операции вывода. Цикп запроса на прерывание и подтверждения прерывания ЦП проверяет наличие запроса па прерывание при прохождении переднего фронта последнего тактового импульса в цикле любой команды. Если обнаруживается запрос на прерывание, то генерируется особый цикл Mj. В тече-ние этого цикла Mi активизируется сигнал IORQ (вместо сигнала MREQ), который указывает устройству, запросившему прерывание, что оно может подать на шнну данных 8-разрядный вектор прерывания. В этот цикл автоматически включается два интервала ожидания, продолжительность каждого

|