| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

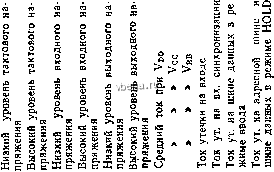

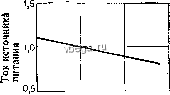

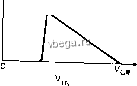

Космонавтика Архитектура 3-х шинных систем а а- ta о I ° I §41 1. о ю S о Т Q, И g g S 2 s > о S - <u S-S 5 а > et S Щ CO И S oo> oV/ u gt5 v/v/v/ > > >s- V/ V/ V/+ Ю (Л Wl M Ю m wi to > > >> и от ca ca ю ca ю CQ < < < <. < < я x x s s s г s s + +a + >° о о о oo-S2 2cf22 8? > > со со  3 S . = g м 14 i-i t-t о > > > > > > о U в л J о о pq и о в состоянии Блокировка или т;ригге) разрешения прерывания сброшен, он не будет реагировать на прерывания. RESET (BxL) Когда сигнал RESET активизируется, счетчик команд очищается. После подачи сигнала RESET ЦП начнет выполнение программы с команды, находящейся в памяти в ячейке с адресом 0. Кроме того, будут сброшены триггеры, определяющие состояния выходов INTE и HLDA. Отметим, что чистка флажков, аккумулятора, указателя стека и регистров не производится. Vss=0 В, VDD--fl2±5% В, Vcc = -b5d=5% В, Vbb=-5±5% В. Ф1, Ф2 - яервая и вторая фазы последовательности тактовых импульсов. Эти входы не совместимы с TTL-схемами. Допустимые предельные значения [8080Л)] Температура окрул<ающсй среды Температура устройства памяти Все входные и выходные напряжения относительно напряжения Vbb Vcc, Vdd и Vss относительно Vbb Мощность рассеяния О- + 70 °С -65--Ь 150 С -0,3-+ 20 В -0,3-+ 20 В 1,5 Вт  МАХ----- О +25 450 +75 Темпеоатуоа окружающей среды (в градусах.Цельсия) Рис. П.2. Зависимость тока источника питания от температуры окружающей среды. Зависимость нормализована: Д1/ДТа=-0,45%ЛС.  Рис. П.З. Зависимость тока утечки шины данных от уровня сигнала DBIN Емкостные характеристики Тд=25°С, Vco = Vdd=Vss=0 В, Vbb=-5 В Таблица 2

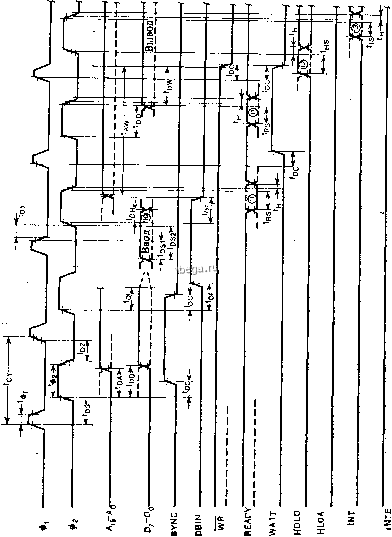

> функционирование устройства при значениях параметров, превышающих предельные, не допускается. Работа устройства при предельных значе- нях указанных параметров в течение длительного времени может изменить кдрактернстнки надежности устройства. to я к 1 -аа 5 S I X С =2 яг - 5 сз 1 m я, 6 g £ II II в- w . £ е log  Таблица 5? Характеристики по переменному току (микропроцессор 8080 А) (Есл\ не оговорено особо, то Та=0 -70*С, Vdd=+12B±5%, Vcc=+5 В±5%, Vbb=-5 В±5%, Vss=0 В.) Обозначение Параиетр Значеиие га . SO Единица измерения Условие проверк tr. tf to, to, too toe tosi Период следования тактовых импульсов Длительность перед, него н заднего фронта тактовых импульсов s*l и Ф2 Ширина импульса 1 Ширина импульса Ф2 Задержка импульса Ф2 по отношению к заднему фронту импульса Ф\ Задержка импульса !*1 по отношению к заднему фронту Ф2 Время задержки им- пульса i*2по отношению к импульсу 1*1 Время задержки по-: дачи адреса относительно импульса. i*2 Время задержки выдачи данных относительно импульса s*2 Задержка подачи сигналов SYNC, WR, WAIT, HLDA по от ношению к переднему фронту импульсов Ф1 и Ф2 Время задержки подачи сигнала DBIN относительно импульса Ф2 Время задержки перехода шнны данных в режим ввода по отношению к переднему фронту импульса Ф2 Время установки данных на шине данных 0,48 60 220 О 2,0 50 0,32 О 50 145 О 2,0 25 0,38 О 60 175 О 2,0 50 НС НС НС Cl-IOO иФ Cl-50 пФ- функциональное описание 8080А/8085А-2 Микропроцессор 8085А представляет собой 8-разрядный ЦП. Для него требу-ется источник питания с напряжением -f5 В. Тактовая частота генератора тактовых импульсов для микропроцессора 8085А равна 3 МГц; а для микропроцессора 8085А-2 - 5 МГц. Таким образом, эти микропроцессоры обладают более высоким быстродействием по сравнению с микропроцессором 8080А. Кроме того, для построения систем, обладающих минимальными возможностями, предусмотрены следующие устройства: ОЗУ/Ю - 8156, ПЗУ/Ю - 8355 или ППЗУ/Ю - 8755А. Микропроцессор 8085А имеет двенадцать 8-разрядных регистров. Четыре из них, разбитые на пары, используются как два 16-разрядных регистра. Шесть других регистров могут использоваться либо как 8-разрядные, либо для образования 16-разрядных регистров. Регистры микропроцессора 8085А имеют следующее назначение: Обозначение АСС или А PC ВС, DE, HL SP F Регистр Аккумулятор Счетчик команд Регистры общего назначения; HL - указатель данных Указатель стека Регистр флажков Содержимое 8 разрядов 16-разрядпый адрес Шесть 8-разрядных, три 16 разрядных 16-разрядный адрес 5 флажков (8 разрядов) В микропроцессоре 8085А использована мультиплексированная шина данных. Адрес передается по двум шинам: старший байт адреса - по шине адреса, а младший байт - по шине данных. В начале каждого машинного цикла младший байт адреса поступает на шину данных. Этот младпшй байт адреса может быть зафиксирован в любом 8-разрядном фиксаторе посредством подачи сигнала отпирания фиксатора адреса (ALE). В остальное время машннно-то цикла шина данных используется для передачи данных между микропроцессором и памятью илн устройствами ввода-вывода. Микропроцессор 8085А вырабатывает для шины управления- сигналы RD, WR, So, Si н Ю/м! Кроме того, он же иыаает сигнал подтверждения прерывания INTA. Сигнал HOLD и все прерывания синхронизируются с помощью внутреннего генератора тактовых сигналов. Для обеспечения простого последовательного интерфейса и микропроцессоре 8085А предусмотрены линия последовательного ввода данных (SID) и линия последонательного вывода данных (SOD). Микропроцессор 8085А имеет также три вывода для маскируемых сигналов прерывания по вектору и один вывод для немаскируемого прерывания TRAP. Прерывания и поспедовательный ввод-вывод Микропроцессор 8085А имеет всего 5 входов для подачи сигналов прерываний: INTR, RST 5.5, RST 6.5, RST 7.5 и TRAP. Сигнал INTR имеет такое же назначение, как и сигнал INT в микропроцессоре 8080А. Каждый из входов RST 5.5, RST 6.5 и RST 7.5 может программно маскироваться. Прерывание по входу TRAP не может быть маскировано. Если маска прерываний ,не установлена, то нз указанные маскируемые прерывания микропроцессор будет реагировать, помещая при этом содержимое счетчика команд в стек и переходя к выполнению программы, адрес которой определяется вектором рестарта Так как прерывание TRAP не может быть маскировано, при появле- НИИ запроси прерывания иа этом входе микропроцессор будет всегда переходить к выполненню программы, указанной вектором рестарй) Среди маскируемых прерываний есть прерывания двух различных типов. Входы снгна110в прерываний RST 5.5 и RST 6.5 являются подобно входам INTR и входу INT микропроцессора 8080 чувствительными к уровню сигнала а время распознавания соответствующих сигналов такое же, как и для сигнала INTR. Вход RST 7.5 является чувствительным к переднему фронту сигнала. Чтобы установить триггер, генерирующий внутренний запрос на прерывание, достаточно подать нмпульс на вход RST 7.5. Триггер запроса прерывания RST 7.5 остается установленным до тех пор, пока прерывание не будет обработано. После завершения обработки прерывания он автоматически сбра- i Внутренние схемы микропроцессора 8085А Запрос на лрерывание RESET IN TRAP RESET -Ь5В- D CLK F/F CLEAR Запрос на прерывание TRAP Подтверждение TRAP R F. запроса на преры-- ванне TRAP Рнс. П.5. Схема приема сигналов TRAP н RESET IN. сывается. Этот триггер также может быть сброшен с помощью команды SIM или посредством подачи сигнала RESET IN на соответствующий вход микропроцессора 8085А. Внутренний триггер запроса прерывания RST 7.5 может быть установлен подачей импульса на вывод RST 7.5 даже тогда, когда прерывание RST 7.5 маскировано. Состояние масок прерываний типа RST может быть изменено только командой SIM и сигналом RESET IN (см. опнсаине команды SIM в гл. 6). Каждому прерыванию приписан некоторый постоянный приоритет: сигнал TRAP имеет наивысший приоритет, затем идут сигналы RST 7.5, RST 6.5, RST 5.5, сигнал INTR имеет низший приоритет. Если на прерывание поступает более чем один запрос, то сначала обрабатывается прерывание, имеющее наивысший приоритет. Эта приоритетная схема не влияет на уже стартовавшие программы обработки прерываний. Но если прерывания разрешены до. окончания выполнения программы обработки прерывания, то при поступлении запроса на прерывание по входу RST 5.5 программа обработки прерывания RST 7.5 прекратит работу. Сигнал прерывания TRAP используется при возникновении катастрофических событий, например при повреждении источника питания или при возникновении неисправностей в шинах системы. Сигнал TRAP распознается системой подобно другим прерываниям, однако он имеет наивысший приоритет. Это прерывание не может быть маскировано. Вход TRAP является чувствительным и по фронту сигнала, и по его уровню. Сигнал TRAP должен выра-

|

||||||||||||||||||||||||||||||