| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

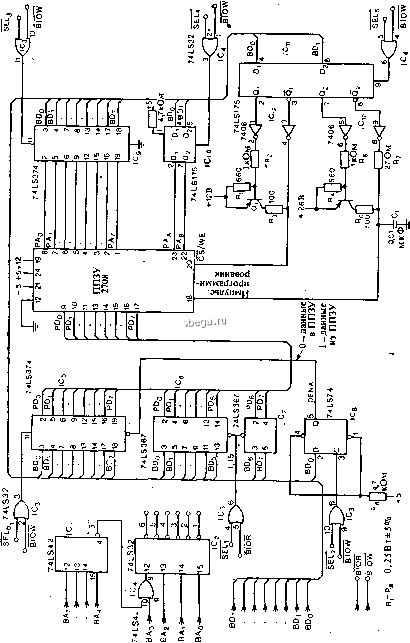

Космонавтика Архитектура 3-х шинных систем Процедура проверки сигнала РАЗРЕШЕНИЕ ЗАПИСИ для блоков ICi7 и ICis 1. Установить адресную шину (ВАр-BAis) в состояние 1000. При этом система переведет сигнал SEL4 в состояние логического 0. Сигнал SEL4 подается на выводы 1 и 4 IC12. 2. Установить с помощью управляющих разрядов УТСС режим, при котором Ю/М соответствует уровню логического 0. Это переводит систему в режим работы с памятью. Сигнал RI> должен соответствовать уровню логической 1 (нерабочее состояние). Сигнал WR должен соответствовать уровню О, что-определяет наличие режима РАЗРЕШЕНИЕ ЗАПИСИ. При этом состоянии управляющих разрядов устанавливается сигнал BMEMW, представляющий собой буферированный сигнал ЗАПИСЬ в память системы. Этот сигнал поступает на вывод 1 Ю12. Отметим, что в соответствии с электрическим состоянием адресной шины сигнал SEL4 находится в состоянии логического О, а буферированный сигнал ЗАПИСЬ в память - также в состоянии О в соответствии с логическим состоянием шины управления. При этих условиях на выводе 6 IC12 поддерживается сигнал уровня логического 0. Заметим, что вывод 6 Ю12 также соединяется с выводом 10 ICi7h Ю1в, поскольку эти устройства, как упоминалось ранее, работают параллельно. 3. Проверить далее наличие уровня логического О на выводе 10 ICi7 и Ю8. как это должно быть. 4. Проверить наличие уровня логической 1 иа выводе 10 Ю19 и Югр. Это определяет наличие сигнала РАЗРЕШЕНИЕ ЗАПИСИ для Ю19 и Ю2Р. Если на шаге 3 или 4 обнаруживается ошибка, необходимо проверить информационный канал от УТСС микропроцессора 8085 к блоку ОЗУ. 5. Проверить подачу сигнала РАЗРЕШЕНИЕ ЗАПИСИ на блоки ICi9 и Ю20. По таблице распределения памяти видно, что адресное пространство Ю19 и IC2P (ОЗУ2) есть 1400-17FF. Установить адресные переключатели таким образом, чтобы на линии адресной шины ВАр-ВА15 был подан адрес 1400i6. При этом сигнал SEL5 с вывода 6 Ю12 принимает логический уровень 0. Сигнал SEL5 подается также на выводы 10 и 13 Ю12. 6. Теперь в системе продолжает поддерживаться сигнал BMEMW. Прн логическом уровне О сигнала на выводах 13 и 12 Ю12 на выводе 11 Ю12 будет также сигнал логического уровня 0. 7. Проверить наличие логического уровня О на выводе 10 Ю19 и Югр. Это рабочий режим для разрешения записи в ОЗУг. 8. Проверить наличие логического уровня 1 на выводе 10 Ю17 и Ю18. Это нерабочий режим для разрешения записи в ОЗУ1. Если на шаге 7 или 8 обнаруживается ошибка, проверить снова информационный канал от ОЗУ к УТСС, чтобы локализовать неисправность в этом канале. Таким образом, осуществлена проверка правильности прохождения сигнала ЗАПИСЬ в ОЗУ1 и ОЗУ2 системы. Проверим правильность прохождения сигнала по линии выбора блока ОЗУ1 и ОЗУг. Эта линия должна находиться в активном состоянии (уровень 0) при чтении данных из ОЗУ или при их записи в ОЗУ. Обсудим процедуру проверки линии выбора блока ОЗУ. Из рис. 10.7 видно, что устройство Ю13 является вентилем И типа 74LS08. Линия выбора блока соединяется с выходом одного из четырех вентилей, скомпонованных в устройстве 74LS08. Ю17 и Ю18 подсоединены к выводу 3 Ida, а IC19 и Ю20 - к выводу 6 IC13. Отметим, что одним входом И вентилей является сигнал РАЗРЕШЕНИЕ ЗАПИСИ в ОЗУ1 или ОЗУг, т. е. с выводом 2 Ю13 связан сигнал РАЗРЕШЕНИЕ ЗАПИСИ в ОЗУь а с выводом 5 Ю13 - такой же сигнал ОЗУг. Необходимо проверить, что при выдаче сигнала РАЗРЕШЕНИЕ ЗАПИСИ в ОЗУ1 или ОЗУ2 системы активизируется требуемая линия выбора блока ОЗУ. Этот факт позволяет осуществить проверку одного режима выбора блока точно таким же образом, как это делалось в случае проверки сигнала разрешения записи в ОЗУ1 или ОЗУ2. Вначале система устанавливается в соответствующий режим для проверки сигнала разрешения записи в ОЗУ1, как это описывалось ранее, и определяется наличие логического уровня сигнала О соответственно выбору блока ОЗУ. Далее система устанавливается в режим подачи сигнала разрешения записи в ОЗУг, как описано выше. Затем проверяется наличие логического уровня О сигнала выбора блока ОЗУ2. Сигнал выбора блока ОЗУ1 и ОЗУг также должен иметь логический уровень О при чтении данных нз ОЗУ1 и ОЗУг. Это означает необходимость перевода системы в соответствующий режим, при котором выполнено условие ЧТЕНИЕ из ОЗУ1 или ОЗУ2. Для этого можно использовать следующую процедуру: 1. Установить системный адрес (ВАр-ВА15) 1000. В результате сигнал SEL4 (вывод 5 Юц) имеет логический уровень 0. Этот сигнал осуществляет выбор ОЗУ1. 2. Установить управляющие разряды УТСС в состояние, соответствующее ЧТЕНИЮ из памяти. Это осуществляется путем установки сигнала Ю/М на логический уровень 0. Сигнал RD принимает значение логического О, а сигнал WR - логиче- ской 1. при этих условиях сигнал BMEMR должен иметь уровень логического 0. При одновременном существовании сигналов BMEMR и SEL4 уровня логического О вывод 3 IC12 будет соответствовать также уровню логического О, что является для системы условием чтения из ОЗУь 3. Проверить наличие логического уровня О сигнала выбора блока на выводе 8 IC17 и ICig. Отметим, что сигнал выбора блока принимает значение логического уровня О, поскольку на ВЫВОД 1 ICi3 подается уровень О вследствие наличия логического уровня О на выводе 3 IC12. 4. Проверить наличие логического уровня 1 сигнала выбора блока ОЗУ2 (нерабочий режим). Если на щаге 3 или 4 обнаруживается ощибка, необходимо локализовать неисправность в системе. 5. Проверить подачу сигнала выбора блока ОЗУ2 при выполнении ЧТЕНИЯ из памяти для ОЗУ2. С этой целью установить адрес 1400 на адресной шине системы (ВАо-ВА15) с помощью УТСС. 6. Система должна быть переведена в режим ЧТЕНИЕ из памяти. Отметим, что при нахождении системы в данном режиме и выдаче сигнала .SEL5 (с помощью адресной шины) на выводе 8 IC12 поддерживается логический уровень 0. В результате на вывод 4 ICi3 также подается логический уровень О, что в свою очередь приводит к поддержанию логического уровня О на выводе 6 IC13. Проверить наличие логического уровня О входного сигнала выбора блока ОЗУ2. 7. Проверить наличие логического уровня 1 сигнала выбора блока ОЗУ1 (нерабочее состояние). Если на шаге 6 или 7 обнаруживается ошибка, необходимо определить местоположение неисправности. Допустим, что описанные выше проверки подтвердили правильность работы технических средств, что определяет правильность соединения адресной шины, а также шины данных с ОЗУ1 и ОЗУ2. Кроме того, шина управления системы осуществляет правильный выбор ОЗУ1 и ОЗУ2 при обраще1нии к памяти для чтения или записи. Наконец, осталось проверить правильность подачи питания на ОЗУ1 и ОЗУ2. При работе статического ОЗУ 2114 используется лишь источник -f5 В, поэтому необходимо проверить наличие уровня напряжения -f 5 В на выводе 18 IC17, ICis, IC19 и IC20. Показав, что источник питания функционирует удовлетворительно, мы тем самым завершаем проверку правильности интерфейса ПЗУ и ОЗУ с микропроцессорной системой на базе устройства 8085, имеющей архитектуру с 3 шинами. 10.10. Отладка интерфейса клавишного; пульта Рассмотрим отладку интерфейса клавишного пульта системы, поскольку мы используем тот жй лульт, который был описан в гл. 4. Подробное обсуждение отладки этого интерфейса было проведено в гл. 5, поэтому повторение описанной там процедуры излишне. Если у читателя возникнут какие-либо вопросы в этом смысле, он сможет обратиться к гл. 5. В этой главе! отладка интерфейса клавишного пульта обсуждалась для системы, создаваемой на базе микропроцессора Z80. В настоящей главе рассматривается система на основе микропроцессора 8085. Однако мы достаточно подробно изучили УТСС для микропроцессора 8085, чтобы провести такую же последовательность проверок, которая была описана в гл. 5 в отношении отладки клавишного пульта системы на базе Z80. 10.11. Отладка интерфейса устройства отображения Подробное описание отладки интерфейса устройства отображения было приведено в гл. 5. В настоящей главе рассматривается точно такое же устройство отображения, что и /в гл. 4. Поэтому, если у читателя имеются какие-либо неясности относительно отладки интерфейса данного устройства, он может обратиться к гл. 5, где соответствующие вопросы обсуждаются достаточно подробно--Изд.ожение материала в гл. 5 ориентировано на микропроцессор Z80. Однако в гл. 10 даются обширные сведения по использованию УТСС для микропроцессора 8085, так что читатель в состоянии осуществить необходимые проверки для микропроцессора 8085 по аналогии с теми, которые описаны в гл. 5 для микропроцессора Z80. 10.12. Отладка схем подключения ППЗУ к системе Рассмотрим теперь отладку схем ввода-вывода, предназначенных для подключения программируемого ППЗУ к системе. Эти схемы представлены на рис. 1,0.12. При обсуждении интерфейса с программируемым ППЗУ для рассматриваемой системы необходимо выделить пять основных функций технических средств системы, а именно: 1. Выдача адреса на программируемое ППЗУ. 2. Ввод и вывод данных ППЗУ; 3. Подача питания на ППЗУ. 4. Подача импульса программирования на ППЗУ. 5. Выдача импульса выбора блока/РАЗРЕШЕНИЕ ЗАПИСИ. Последние две функции описаны в отдельных разделах на-стоящейглавы. Рассмотрим выдачу адреса на программируе-  т С С а та в о о. с о S га 3 ш га S а ч Из схемы рис. 10.12 видно, что выдача адреса на ППЗУ осуществляется посредством двух двоичных фиксаторов - ICg и ICio. Устройство ICg есть 8-раарядный фиксатор типа 74LS374, а ICio -4-разрядный фиксатор типа 74LS175. Отметим, что входом для 74LS374 являются линии BDo-BD7, а для 74LS175-линии BDo-BDi. Это говорит о возможности пере- 74LS42 BAs ВА, ВАл 12 13 14 15 4 74LS32 74LS42 -О SEL5 -о SEL< -О SEL, -О SEL, -о SEL, -OSEL, Рис. 10.13. Часть схемы рис. 10.12, генерирующая код выбора. дачи 10-разрядного адреса ППЗУ, что согласуется с потребностями ППЗУ 1 КХ8, для которого необходимо 10 адресных линий. Устройство 74LS374 ICg формирует младший байт адреса ППЗУ, а устройство 74LS175 -два старших разряда адреса. Отметим, что синхронизация 8-разрядного фиксатора 74LS374 осуществляется с вывода 11 IC3. Сигнал на этом выводе имеет логический уровень О, если одновременно имеют уровень О сигналы на выводах 12 (SEL3) и 13 (BIOW). Такие условия создаются, когда адресная шина переводит сигнал SEL3 к уровню логического О, а шина управления генерирует буферированный сигнал записи при вводе-выводе (BIOW). Рассмотрим генерирование сигнала SEL3 с помощью технических средств.

|