| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

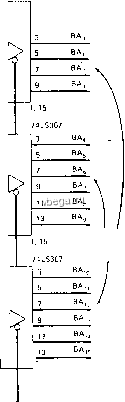

Космонавтика Архитектура 3-х шинных систем Микропроцессор 8080 74L.S367 Буфер адреса 1,мп / Характеристики ЦП Z80 по постоянному току Тл-О-УОС, Усе-+5 В±5%, если ие оговорено о >бо Буферированный выход Ао в систему Рис. 2.8. Ток на выходе адресной линии микропроцессора должен быть согласован по величине с током на входе буфера адреса. В приведенном примере соответствующие значения тока составляют 0,4 мА для состояния логического О (1шо) и 20 мкА для состояния логической 1 (Iini)- Направление тока показано стрелками. Микропроцессор 8080 А А,: А, А А, 74LS367

Буферированные адресные линии Выводы 1 и 15 всех устройств 74LS367 Рис. 2.9. Полная схема адресной шины микропроцессора 8080 с устройством 74LS3e7, используемым в качестве буфера адресных линий.

Рис. 2.10. Спецификации адресных выходов мшсропроцессора Z80 и некоторые другие спецификации по постоянному току. Напряжение иа адресных выходах обозначено как Vc . и Уон. (С разрешения фирмы Zilog.) 2.5. Адресная шина Z80 Покажем, каким образом можно построить буферы для адресной шины микропроцессора Z80. Спецификации адресных входов Z80 приведены на рис. 2.10. Из этого рисунка видно, что для адресных выходов Z80 характерно наличие тока 150 мкА в состоянии логической 1 и 2 мА в состоянии логического 0. Допустим, что адресная шина системы характеризуется нагрузкой 200 мкА в состоянии 1 и 3 мА -в состоянии 0. Как видно, в этом случае микропроцессор Z80 не в состоянии управлять адресной шиной. Заметим, снова, что подобные условия выбраны с целью сделать необходимым введение буфера адреса. Выберем в качестве буферов адреса устройства 74LS367. Полная схема соединений для буферированной адресной шины микропроцессора Z80 приведена на рис. 2.11. Ввиду простоты

Микропроцессор Z80 ЗТ 74LS3e7

1,15 74LS367 3 I. 15 Буферированные адресные шины 74LS367

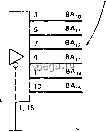

Рис 2 11. Полная схема адресной шниы микропроцессора Z80 с устройством 74LS367, используемым в качестве буфера адреса. интерфейса Z80 с микропроцессорной системой дальнейшее рассмотрение адресной шины Z80 нецелесообразно. Отметим, что адресная шина Z80, как и 8080, состоит из 16 линий (рис. 2.9). 2.6. Адресная шина 6800 Спецификации для выходных адресных линий микропроцессора 6800 приведены на рис. 2.12, из которого видно, что нагрузка для этих линий составляет 2 мА для состояния логической 1 я 150 мкА для состояния логического 0. Допустим, что нагрузка по току в адресной шине проектируемой системы превышает возможности микропроцессора 6800, т. е. необходимо буферирЬ-вание адресных выходов микропроцессора 6800. В качестве буферов адреса снова используем устройство 74LS367. Полная схема буферированной адресной шины микропроцессора 6800 приведена на рис. 2.13. Из этой схемы видно, что адресная шина 6800, подобно шинам 8080 и Z80, состоит из 16 линий. 2.7. Адресная шина микропроцессора 8085 Адресная шина микропроцессора 8085 по своему построению отличается от уже рассмотренных шин. Для адресных шин устройств Z80, 8080, 6800 характерно то, что каждой линии шины соответствует специальный вывод в корпусе микропроцессора. Это означает, что вне зависимости от состояния микропроцессора вывод АО всегда соответствует разряду адресной шины Ао, что упрощает формирование 16-разрядного адреса. Здесь просто группируются 16 выводов микропроцессора, и эта группа определяется как адресная шина системы. В устройстве 8085 используется другой принцип, основанный на временном мультиплексировании функций выводов, когда одни и те же выводы в разные моменты времени представляют разные функции. Это позволяет реализовать ряд дополнительных функций при тех же 40 выводах в корпусе микропроцессора. Восемь мультиплексированных выводов устройства 8085 играют роль шины данных либо младших разрядов адресной шины. В некоторые моменты эти восемь физических выводов передают адрес, в другие моменты они используются для ввода или вывода данных. Как показано на рис. 2.14 выводы в микропроцессоре 8085 обозначаются как ADq-AD7. , Из рис. 2.14 видно, что старшие восемь разрядов адресной шины системы As-А15 соответствуют аналогичным адресным выводам предыдущих микропроцессоров, т. е. каждый вывод предназначен лишь для реализации соответствующего разряда адреса. Mceaoo о, Тд = о * 70°С, если ие оговорено особо)

а) За исключевием IRQ и NMI. требующих согласующих резисторов сопротивлением ЗкОм для обеспечения нагрузочной способности точечного ИЛИ-соединевия в оптимальном режиме 6) Емкость периодически замеряется Рис. 2.12. Спецификации адресных выходов микропроцессора 6800. На адресных выходах дано напряжение высокого н низкого, уровня сигнала. (С раз-.решення фирмы Motorola.) Ввиду ТОГО ЧТО в микропроцессоре 8085 используются мультиплексированные выводы для адреса и данных, формирование младших восьми разрядов адресной шины пр сравнению с ра- Микролроцессор 6800 15 74LS367 1, 15 7413367 1, 15 В At 1 IS I 74LS367 3 BA,j ВА,5 Рис. 2.13. Полная схема адресной шины микропроцессора 6800 t устрой- ством 74LS367, используемым в качестве буфера адреса. нее рассмотренными микропроцессорами несколько усложняет- ся. Главная особенность заключается в необходимости (фиксации логического состояния выводов ADo-AD7 микропроцессора 8085 в моменты, когда они функционально представляют адресные разряды Ао-А7. Для этого необходимо точно знать когда на этих выводах отображается адресная информация. В корпусе 8085 существует специальный вывод {Ш 30), обозначаемый ALE (Address Latch Enable) - открытие фиксатора адреса, сигнал на котором в нормальном состоянии соответст--

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||