| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

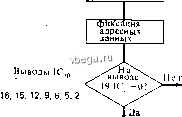

Космонавтика Архитектура 3-х шинных систем 5(1 Sji Sj, S4, Sj, Sg, S7 Выводы 1С 16, 15, 12, 9, 6, 5,2 Нача-ло S0-S7 = О на УТСС ALE = 1 ALE = О Фиксация адресных Si.Sj.Sj.S.Ss.Sg.S, So = 0 Фиксация адресных данных  Определение причины  Определение причины Повторить для S,-S: Рис. 10.9. Блок-схема алгоритма проверки выходов ВАо - ВА7 адресной шины. ЦИИ адресных данных. В случае неверной реализации функции мы можем разложить эту функцию на микро-шаги с целью локализации неисправности. На рис. 10.9 приведена блок-схема, отражающая основные этапы проверки адресных линий ВАо-ВА7. 10.5. Отладка шины управления системы Обратимся теперь к проверке с помощью УТСС .шины управления системы. Шина управления представлена на схеме рис. 10.10, которая является частью общей схемы рис. 10.7, что сделано с целью облегчить последующее обсуждение. В дальнейшем следует еще раз изучить схему рис. 0.7, чтобы убе- LS04 1f\ 2 - 31 =Е> LS32 -О BIOR -О BIOW -о BMEMR -о BMEMW LS125 1С, Рис. 10.10. Часть схемы рис. 10.7, определяющая шину управления системы. диться В правильном понимании роли схемы шины управления, приведённой на рис. 10.10, в системе. При настройке шины управления системы будем использовать упранляющие переключатели УТСС, помеченные как RD, WR, Ю/М. Из рис. 10.10 видно, что эти три сигнала являются входами для комбинационной логической схемы, включающей шину управления системы. Управляющие сигналы вырабатываются вентилем ИЛИ схемы IC5 и инвертором схемы Юе. Перед вводом в систему эти сигналы буферируютея устройством 74LS125 IC7. При настройке шины управления системы может быть использована следующая процедура. Процедура настройки шины управления системы 1. Установить управляющие переключатели, помеченные как JRD, WR, IO/M, в следующие положения: а) RD = логическая 1 (нерабочее состояние); б) WR = логический О (нерабочее состояние); в) Ю/М = логическая 1 (режим ввода-вывода). 2. При указанном положении переключателей на всех выходах щины управления системы должен быть сигнал уровня логической 1. Проверить наличие сигнала уровня логической 1 на выводах 3, 6, 8 и IJ устройства 74LS125 IC7. 3. Установить в состояние О переключатель, помеченный.как WR, что соответствует подаче управляющего сигнала BIOW. Проверить наличие напряжения логического уровня О на выводе 6 IC7 (BIOW). 4. Проверить наличие напряжения логического уровня 1 на выводах 3, 8 и 11 IC7 (нерабочее состояние). 5. При проверке функционирования каждой линии шины необходимо помнить, что на основании результатов предыдущего обсуждения сигналы этих линий являются взаимоисключающими. Это означает, что одновременно сигнал не может быть подан ни на какие дВе линии. 6. Установить переключатель WR в положение, соответствующее логическрй 1. 7. Установить переключатель RD в положение, соответетву-ющее логическому О, что соответствует подаче управляющего сигнала BIOR. 8. Проверить, что логический уровень напряжения О имеет единственный управляющий сигнал BIOR на выводе 3 IC7. 9. Установить переключатель RD в положение, соответствующее логической 1. 10. Теперь проверена правильность прохождения сигналов BIOW и BIOR. И. Установить управляющий переключатель Ю/М в положение, соответствующее логическому О, что переводит шину управления в режим работы с памятью. 12. Установить переключатель WR в положение, соответст-вующее логическому О, что соответствует подаче сигнала BMEMW. Проверить наличие напряжения логического уровня О сигнала BMEMW на выводе 11 IC7. 13. Проверить наличие напряжения логического уровня 1 сигналов BIOR, BIOW, BMEMR. 14. Установить переключатель WR в положение, соответствующее логической 1. 15. Установить переключатель RD в положение, соответствующее логическому 0 что соответствует подачке сигнала BMEMR. Проверить наличие напряжения логического уровня О сигнала BMEMR на выводе 8 IC7. 16. Проверить наличие напряжения логического уровня 1 управляющих сигналов BMEMW, BIOW, BIOR. 17, Установить переключатель RD в положение, соответствующее логической 1. Теперь установлено, что выходные управляющие сигналы системы правильно отражают входные воздействия микропроцессора 8085. Если на каком-то шаге процедуры будет обнаружено нарушение этого соответствия, можно легко осуществить статическую проверку логических сигналов и локализовать неисправность. 10.6. Отладка шины данных системы Рассмотрим теперь отладку шины данных системы с помощью УТСС. Приведем процедуру определения возможности двунаправленной передачи данных по шине данных, проверив буферирование шины данных и внешние устройства. Процедура проверки канала выдачи данных 1. Установить управляющие переключатели RD и WR УТСС в положения: а) RD = логическая 1; б) WR = логическая 1. При этих условиях существует канал из УТСС микропроцессора 8085 к тестируемой системе. УТСС функционирует в режиме вывода данных, аналогичном соответствующему режиму микропроцессора 8085. 2. Установить переключатели УТСС, помеченные как So-Sr, в положение, соответствующее логическому 0. 3. Установить переключатель So в положение, соответствующее логической 1. 4. Проверить наличие напряжения логического уровня 1 на выходе BDo (вывод 2 IC3). 5. Установить переключатель So в положение, соответствующее логическому 0. Проверить наличие напряжения логического уровня О на выходе BDo (вывод 2 IC3). 6. Повторить шаги 3-5 для всех линий шины данных DBi- DB7. 7. На каждом шаге проверить правильность функционирования линий шины данных при выводе информации путем измерения напряжения логических уровней. Если выходные сигналы на шине данных на некотором шаге процедуры не являются корректными, необходимо статически проверить уровни напряжения постоянного тока с целью определить причины неисправности. Это достигается путем проверки статических электрических сигналов на протяжении информационного канала. Успешное завершение процедуры означает, что шина данных системы при выводе данных функционирует правильно, т. е. шина данных должна выводить данные, соответствующие правильным сигналам от микропроцессора 8085. Теперь проверим правильность функционирования шины данных в режиме ввода и покажем, каким образом можно проверить информя-ционный канал от тестируемой системы к УТСС, чтобы убедиться в правильности его работы. Процедура проверки канала ввода шины данных 1. Установить переключатели УТСС, помеченные как So- Sr, в положение, соответствующее логическому 0. 2. Установить адресные линии системы ВАо-ва15 в состояние 0. Начало Установить УТСС в режим ЧТЕНИЕ с устройства ввода-вывода Все светоизглуч. диоды на УТСС включены? Заземлить линию BDq шины данных 01,02,03,04, Dg.De.Oy Определение причины Светоизлуч. диоды выключены? Определение причины Повторить для BDj-BD, Рис. 10.11. Укрупненная блок-схема алгоритма проверки сигналов BDj -ВО шины данных системы. 3. Установить управляющие переключатели в положения: а) RD = логическая 1; б) WR=логическая 1; в) Ю/М = логическая 1 (режим ввода-вывода). 4. При указанном режиме управляющих переключателей светоизлучающие диоды выключены. 5. Установить переключатель RD в положение, соответствующее логическому 0. Теперь все светоизлучающие диоды должны зажечься, поскольку шина данных отключается. Тем самым никакое устройство вывода не управляет линиями шины данных. Входы устройств 74L04 1С& и Юд УТСС отключены, а отключение входа TTL-схемы соответствует логическому уровню 1. 6. Взять проволочную перемычку и заземлить один ее конец. 7. Соединить другой конец перемычки с линией BDo шины данных, что соответствует выводу 2 Юз. Это позволяет, подать на шину данных логический сигнал уровня О (заземление). 8. Проверить, что светоизлучающий диод УТСС, помеченный как Do, выключен. 9. Заземлить поочередно линии шины данных BDi-BD7, проверяя выключение соответствующих светоизлучающих диодов. Блок-схема описанной процедуры представлена на рис. 10.11. Теперь рассмотрены процедуры проверки шин адресной, данных и управления системы. Эти шины будут правильно функционировать при правильном поступлении сигналов от микропроцессора 8085. Однако мы не осуществили проверок правильности соединения шин системы с другими схемами системы. Такие проверки будут выполнены в процессе дальнейшего обсуждения. 10.7. Проверка схемдешифрирования выбора памяти Перейдем к проверке технических средств, предназначенных для дешифрирования адреса памяти. Логические схемы дешифрирования сигнала выбора памяти для системы, приведенной на рис. 10.7, представлены блоком Юц, являющимся устройством 74LS42. Принцип действия устройства 74LS42 заключается в подаче выходного сигнала О на вывод, соответствующий каждому входу. При этом выводы 1, 2, 3, 4, 5, 6, 7 соответствуют двоичным входам О, 1, 2. 3, 4, 5, 6 соответственно. Допустим, что код двоичного ООП подан на выводы устройства 74LS42 12, 13, 14 и 15 соответственно (это соответствует двоичному входу 3). Вывод 4 устройства 74LS42 теперь находится в состоянии логического 0.

|