| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

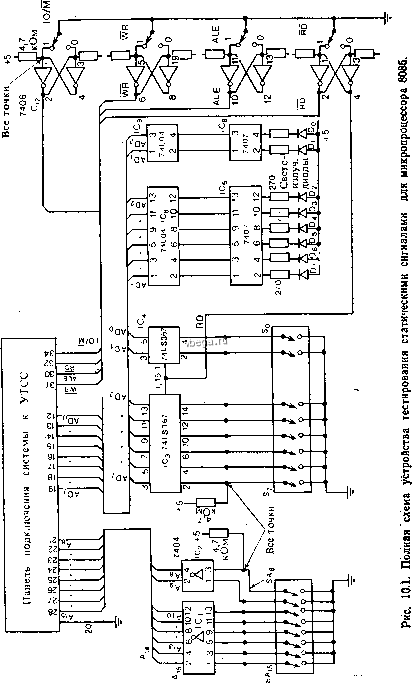

Космонавтика Архитектура 3-х шинных систем  дартиых логических схем. Как видно из рис. 10.1, для этого достаточно использовать лишь пять различных ИС. Во-вторых, тестирование посредством статических сигналов-чрезвычайно удобно в применении. Отметим, что устройство-тестирования осуществляет управление системой точно так же, как и микропроцессор. Поэтому для использования устройства тестирования посредством статических сигналов (УТСС) необходимо лншь понять особенности управления техническими средствами системы со стороны микропроцессора. В-третьих, УТСС можно приспособить к особенностям конкретной системы. Простота технических средств УТСС позволяет модифицировать это устройство с целью реализации специальной функции, присущей лишь конкретной системе. Пользователь может по желанию вносить изменения в УТСС. Об этом свидетельствует тот факт, что фирма CMS поставляет версии УТСС для любого из микропроцессоров, рассмотренных в книге. 10.2. Устройство тестирования посредством статических сигналов для микропроцессора 8085 Рассмотрим функционирование УТСС, показанного на рис. 10.1, детально проанализировав назначение каждого компонента схемы. На рис. 10.1 можно заметить переключатели SAis-SAg. Каждый из них одним концом соединяется с землей, а другим - с согласующим резистором на 4,7 Ом, ак это показано на рис. 10.1 лишь для переключателя SAg. Переключатели расположены на входах интегральных схем ICi и Юг (рис. 10.1), представляющих собой устройства 7404. Выходами ICi и ICj являются адресные выходы Ais-As для микропроцессора 8085. При разомкнутых переключателях входы ICi и IC2 - в состоянии логической 1, которое является результатом воздействия источника питания в 5 В через согласующий резистор 4,7 кОм. При замыкании переключателей входы ICi и IC2 заземляются, что соответствует сигналу логического 0. Функционирование переключателей SA15-SAg может быть в общем виде представлено следующим образом. В одном положении переключателей на соответствующие выходы ICi или IC2 поступает сигнал уровня логической 1, в другом положении -сигнал уровня логического 0. Таким образом выходные линии Ai5-Ag можно по желанию устанавливать в состояние О или 1. При этом сигнал в систему поступает точно так же, как сигнал, выдаваемый микропроцессором 8085 на адресные линии, за исключением того, что соответствующий уровень логического сигнала для обеспечения отладки системы может поддерживаться произвольно долго. Рассмотрим теперь блок вывода данных УТСС. Этот блок- фрагмент рис. 10.1 и отдельно представлен на рис. 10.2. Отме- ТИМ, что переключатели So-S7 подсоединены точно так же, как ранее рассмотренные переключатели SAis-SAs, т. е. размещены на входе устройств 74LS367 IC3 и IC4. Выбор этих интегральных схем обусловлен использованием некоторых устройств с тремя состояниями для вывода данных. Необходимость по- Панель подключения системы 19 18 17 16 15 14 13 12

О О < < о < < < 1,7 кОм IC374LS367 Все точки 1, 15 1 74LS367 9 9 9 9 9 9 Рис 10 2 Часть схемы рис. 10.1, отображающая блок вывода данных утес 8085. следних связана с обеспечением возможности ввода данных в утес, что аналогично вводу в микропроцессор 8085, когда линии данных выступают в качестве входных. Поэтому следует заблокировать выдачу данных УТСС формирователями IC3 и IC4 на время операции чтения, выполняемой УТСС, чтобы не создавать помех при вводе. Блокировка выдачи данных формирователями осуществляется посредствоз! управляющего сигнала RD. Линия подачи этого сигнала показана справа на рис. 10.2. Ниже будет показано, как этот сигнал вырабатывается. Теперь же важно понять лишь то, что выдача данных формирователями на время выполнения УТСС операции чтения блокируется. Во время выполнения УТСС операции чтения данных вводятся в УТСС из тестируемой системы. Для проверки правильности вводимых данных используются индикаторы на светоизлучающих диодах. Схема включения этих индикаторов приведена на рис. 1,0.3. Отметим, что все входы устройств 74L04 ICs-и IC9 подсоединены к отдельным линиям шины данных. Логи- Вхол с ШННЫ- данных

1 3 5 9 11 13 74L04ICs 2 4 6 8 10 12 1 3 74L04 1 3 5 9 11 13 7407 2 4 6 8 10 12

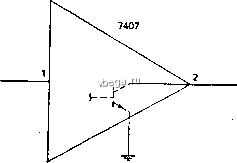

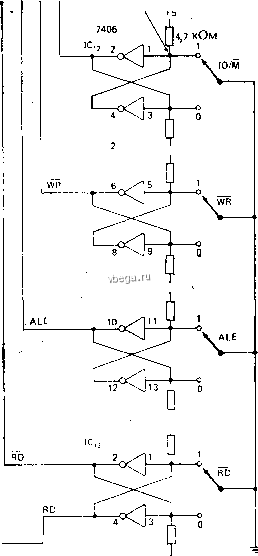

Свето- DrA А Do Рис. 10.3. Часть схемы рис. 10.1, отображающая блок вывода сигналов на светоизлучающие диоды УТСС 8085. ческие сигналы линий данных отображаются посредством показанных на рис. 10.3 светоизлучающих диодов. Если на вход ICs и IC9 подается сигнал 1, то на соответствующем выходе устройства 74L04 формируется сигнал 0. Выход 74L04 соединен со входом 7407 (IC5 и ICe), являющимся буфером со свободным коллектором. В случае сигнала О на входе 7407 на выходе также присутствует сигнал 0. Из теории устройств со свободным коллектором известно, что выход устройства 7407 может быть представлен в виде, изображенном на рис. 10.4. Ясно, что если на вход 7407 поступает сигнал О, то транзистор открывается, в результате от коллектора к эмиттеру на землю протекает ток. Обращаясь снова к рис. 10.3, видим, что светоизлучающий диод анодом подключен к источнику +5 В, а катодом - к выходу устройства 7407 через резистор 270 Ом. Если на выходе устройства 7407 имеется сигнал О, резистор соединяется с землей, в результате через светоизлучающий диод ОТ анода к катоду протекает ток от источника В. При этих условиях последний имеет прямое смещение и излучает свет. £сли /же на выходах устройств 7407, IC5 и ICe, имеется сигнал 1, транзистор на рис. 10.4 закрывается, в результате происходит разъединение с землей резистора, подсоединенного к коллектору. При этих условиях ток через светоизлучающий диод не протекает и последний выключается. Из проведенного обсуждения видно, что светоизлучающий диод включается при сигнале уровня логической 1 на соответ-  Рис. 10.4. Схема устройства 7407, пока,эывающая выходной транзистор, используемый для отвода тока при включении светоизлучающих диодов. ствующей линии шины данных и выключается при сигнале уровня логического 0. Это позволяет визуально наблюдать логическое состояние шины данных в любой момент времени. Отметим, что в УТСС на входе с шины данных имеется устройство 74L04, что видно из рис. 10.3. Может возникнуть вопрос, почему на входе включается инвертор и далее устройство 7407 и нельзя ли применить устройство 7406 для реализации функций устройств 74L04 и 7407? Принятое решение мотивируется тем, что устройство 74L04 потребляет на входе ток 0,1 мА в состоянии логического О и 4 мкА -в состоянии логической 1. Именно такой ток потребляется при работе с шиной данных. Любое устройство, используемое в УТСС, является дополнительной нагрузкой для шины данных. Поэтому допольгатель-ная нагрузка, создаваемая монитором, должна быть по возможности минимальной. Устройство 7406, используемое в качестве входного монитора, создает для шины данных большую нагрузку, чем устройство 74L04, поскольку потребляет на входе ток 1,6 мА в состоянии логического О и 40 мА в состоянии логической 1. Поэтому применение устройств 74L04 и 7407 вместо 7406 позволяет снизить нагрузку на шину со стороны УТСС на порядок, что вполне оправдывает схемную избыточность. Все точки  Рис. 10.5. Часть схемы рис. 10.1, отображающая блок УТСС, предназначенный для регулирования логического уровня управляющих разрядов микропроцессора 8085. Из рис. 10.3 видно, что светоизлучающие диоды постоянно контролируют и отображают логическое состояние линий шины данных, как во время выполнения операции ЧТЕНИЕ, так и при операции ЗАПИСЬ. Прн операции ЧТЕНИЕ отображаются

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||