| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

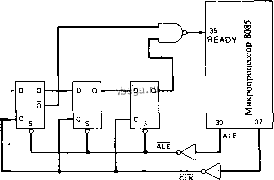

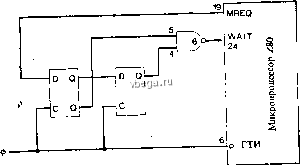

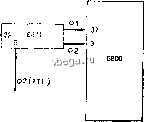

Космонавтика Архитектура 3-х шинных систем ваемой схемы. Для схемы, показанной на рис. 6.23, этот сигнал является выходным. Предположим, что когда схема начинает работать, все ее триггеры на выходах Q имеют уровень логической 1. Справедливость этого предположения мы обсудим ниже. Анализируя временную диаграмму, представленную на рис. 6.25, мы видим, что сигнал запрос ожидания на входе D первого триггера рассматриваемой схемы переходит к уровню логического О, прежде чем сигнал генератора тактовых импульсов перейдет к уровню логической 1. Указанное временное соотношение между этими сигналами выполняется в каждом из трех обсуждаемых сейчас микропроцессоров; оно обеспечивается синхронизацией самих микропроцессоров. Когда синхронизирующий импульс изменяется от уровня логического О до уровня логической 1, выход Q первого триггера типа D переходит в состояние логического О, а выход Q этого же триггера переходит в состояние логической 1. При этом на обоих входах вен-, тиля НЕ И, т. е. на выводах 1 и 2 схемы типа 7400, будет уровень логической 1. Следовательно, на выходе этого вентиля - вывод 3 схемы 7400 -установится уровень логического 0. Сигнал на выводе 3 схемы 7400 также представлен на временной диаграмме, изображенной на рис. 6.25. Отметим, что уровни рассмотренных сигналов остаются постоянными в течение времени существования второго импульса, показанного на временной диаграмме. Во время нарастания переднего фронта третьего синхронизирующего импульса происходит следующее. На выходе Q третьего триггера типа D появится уровень логического 0; такой же уровень, очевидно, будет и на выходе 2 схемы 7400. Теперь вывод 3 схемы 7400 перейдет в состояние логической 1. Когда на этом выводе происходит переход к уровню логической 1, со входа микропроцессора снимается сигнал запроса ожидания. После снятия этого сигнала микропроцессор продолжит работу на нормальной системной скорости. При переходе микропроцессора к нормальному режиму работы все триггеры рассматриваемой схемы устанавливаются в состояние 11 посредством подачи сигнала низкого уровня на входы сброс . Сигнал низкого уровня подается на входы сброс в начале каждого нового машинного цикла микропроцессоров 8080 или 8085. Теперь схема готова к приему сигнала запрос ожидания ; в зависимости от адреса, поступающего по адресной шине, на выходе схемы, представленной на рис. 6.24, установится состояние логического О или состояние логической 1. Схема, изображенная на рис. 6.24, подключается к микропроцессорам 8080 и 8085 так, как это показано на рис. 6.26 и рис. 6.27 соответственно. При этом вывод 3 схемы 7400 (см. рис. 6.24) соединяется со входом RDYIN генератора тактовых RDYIN Генератор тактовых НМПУЛЬСОР 8224 READY WAIT REQUEST D Q 7474 0 Q 7474 0 Q 7474 С VlHKponponeccop 8080 Рис. 6.26. Схема соедниеиия микропроцессора 8080 со схемой, показанной на рнс. 6.24.  WAIT REQUEST. Рнс 627 Схема соединения микропроцессора 8085 со схемой, показанной на рис. 6.24.  !Рис 6 28 Схема соединения микропроцессора Z80 со схемой, показанной на рнс. 6.24. импульсов 8224 микропроцессора 8080 или со входом READY микропроцессора 8085. На схему, показанную на рис. 6.24, синхроимпульсы поступают с выхода 952TTL генератора тактовых импульсов 8224 микропроцессора 8080, При использовании микропроцессора 8085 синхроимпульсы с выхода СLK сначала поступают на инвертор, а после инвертирования - на вход подключаемой к микропроцессору схемы (см. рис. 6.27). Для установки триггеров рассматриваемой схемы в состояние I используется сигнал STSTB - строб состояния -в микропроцессоре 808Q и сигнал ALE - отпирание фиксатора адреса -в микропроцессоре 8085. Схема генерации сигнала запрос ожидания для микропроцессора 280 представлена на рис. 6.28. Отметим, что эта схема работает точно так же, как и схема, рассмотренная нами выше. В данной схеме выход второго триггера соединяется с выводом 4 вентиля НЕ И. Эта схема обеспечивает формирование сигнала запрос ожидания , длительность которого равна только одному периоду последовательности тактовых импульсов. Сигнал запроса ожидания на вход триггера типа D поступает с выхода микропроцессора MREQ. Для подачи синхроимпульсов используется линия, по которой поступают синхроимпульсы на вывод 6 микропроцессора Z80. Перевод в состояние ожидания микропроцессора 6800 В отличие от микропроцессоров 8080, 8085 и Z80 микропроцессор 6800 не имеет входов для приема сигналов READY или WAIT. Способ замедления микропроцессора 6800 при обращении к памяти или к устройствам ввода-вывода носит название растягивания синхронизирующих импульсов . Используя этот способ, фактически можно увеличивать ширину импульса последовательности Ф2 до необходимой величины, определяемой временем доступа к памяти определенного типа. Согласно спецификациям, ширина импульса Ф2 для микропроцессора 6800 не может превышать 4,5 мкс. Если увеличить ширину импульса Ф2, то в микропроцессоре 6800 может произойти потеря информации. Это ограничение необходимо учитывать при растягивании импульса Ф2. В генераторе тактовых импульсов 6871, предназначенном для использования с микропроцессором 6800, предусмотрен вход, который посредством подачи на него сигнала позволяет замедлить или остановить импульс Ф2, т. е. оставить его в данном состоянии, пока на входе действует сигнал запроса. Вход генератора 6871, используемый для этого, называется входом (линией) готовности памяти. Когда на линии готовности памяти низкий уровень напряжения, на входе Ф1 микропроцессора бу- Запрос WAIT Готовность памяти Д1> Одновибратор 02(TTL) 1 г Ширина импульса, вырабатываемого одновибратором  Рис. 6,29. Схема генерации состояния ожидания микропроцессора 6800. Ждущий мультивибратор (одновибратор) запускается задним фронтом поступающего на его вход импульса. Сигнал, запускающий мультивибратор, поступит на его вход, когда и сигнал запрос ожидания , и сигнал Ф2ТТЪ, являющийся выходным сигналом генератора 6871, переходят к уровню логической 1. Когда указанные- сигналы достигнут уровня логической 1, произойдет запуск ждущего мультивибратора и на его выходе появится уровень логического 0. Описанные изменения сигналов иллюстрируются временнбй диаграммой, представленной на рис. 6.30. Вместе с переходом к состоянию логического О выхода ждущего мультивибратора такое же состояние устанавливается и на линии готовности памяти. При этом последовательности тактовых импульсов замораживаются таким образом, что на входе Ф1 микропроцессора устанавливается состояние логического О, а на входе 92 - состояние логической 1. Через определенное время на выходе мультивибратора, а значит, и на линии готовности памяти установится уровень логической 1. Теперь генератор тактовых импульсов продолжит работу в нор- мальном режиме. Вспомним, что в микропроцессоре 6800 все действия на шиие данных происходят при прохождении заднего фронта импульсов последовательности Ф2. Это означает, что и передача данных на устройства вывода, и ввод данных в микропроцессор 6800 стробируются по заднему фронту импульсов фазы Ф 2. Поэтому и осуществляется задержка перехода импульса 0 2 к уров- дет стояние логического О, а на входе 02 -состояние логической 1. Для возобновления нормального режима работы генератора тактовых импульсов и, следовательно, всей системы необ--ходимо подать на линию готовности памяти уровень логической 1. Чтобы обратиться к медленнодействующей памяти, достаточно установить уровень логического О на линии готовности памяти. Схема, предназначенная для этого, представлена на рис. 6.29. НЮ логического О на время, задаваемое ждущим мультивибратором. Это время не должно превышать 4,5 мкс. Кроме того, отметим, что, когда сигнал 52 переходит к уровню логической 1, сигнал на линии готовности памяти перейдет к уровню логического О, на входе Ф2 уровень логической 1 €удет сохраняться, пока ждущий мультивибратор находится в неустойчивом состоянии. После возвращения мультивибратора Запрос WAIT l>2(TTL)/ Запуск одновиёратора у , Ширина \\ импульса Готовность памяти Рис. 6.30. Временная диаграмма сигналов, действующих в схеме генерации состояния ожидания микропроцессора 6800 (см. рис. 6.29). /ф2 к 6800 - Ширина импульса, вырабатываемого одновибратором В устойчивое состояние линия готовности памяти переходит в состояние логической 1 (см. рис. 6.30), а выход Ф2 генератора тактовых импульсов 6871 -в состояние логического 0. Когда сигнал Ф2 переходит к уровню логического О, микропроцессор .6800 коИтролнрует данные на шине данных или память принимает данные на свои входы. Итак, мы рассмотрели способы перевода микропроцессоров 8080, 8085, Z80 и 6800 в состояние ожидания. Следует иметь в виду, что эти способы, конечно, не являются единственными. Представленные здесь схемы являются лишь примерами, которые позволяют нам увидеть, как с помощью аппаратных средств решается задача перевода микропроцессора в состояние ожидания. Хорошо понимая, что необходимо для перевода микропроцессора в состояние ожидания, легко и понять, как в системе работают аппаратные средства, обеспечивающие это состояние, и разработать схему для решения подобной частной проблемы. Кроме того, отметим, что существует другое решение этой задачи, которое может применяться пО желанию. Это решение гораздо проще рассмотренных, однако не всегда может быть использовано. Оно заключается в уменьшении частоты генератора тактовых импульсов микропроцессорной системы. Если микропроцессор работает слишком быстро и вследствие этого-невозможно обеспечить интерфейс памяти стандартного типа, то можно просто уменьшить быстродействие микропроцессора тем самым без использования какого-либо дополнительного Оборудования обеспечить достаточное время для обращения к медленнодействующей памяти. На первый взгляд это решение полностью неприемлемо. Однако требуемое время обращения к медленнодействующим устройствам обычно только на несколько сотен наносекунд больше, чем время, выделяемое для этого микропроцессором. И хотя уменьшение частоты генератора тактовых импульсов приводит к увеличению общего времени выполнения программы, при этом сокращается объем системных аппаратных средств. Естественно, в этом случае приходится все хорошо продумать. Однако отбрасывать это решение без предварительного анализа не следует никогда. Существует много приложений, в которых быстродействие микропроцессора не является определяющим. Тогда его уменьшение может оказаться выгодным - оно, быть может, приведет к желаемому уменьшению объема оборудования микропроцессорной системы. 6.9. Прямой доступ к памяти в микропроцессорах 8080, 8085, Z80 и 6800 Теперь обсудим, как при использовании рассматриваемых нами микропроцессоров реализуется прямой доступ к памяти (ПДП). В режиме прямого доступа к памяти не используется принцип Процессор I Рис. 6.31. Схема связи двух микропроцессоров с памятью системы. Процессор 2 Память системьг Адресная шИиа lUifHii данных Пина управления I Примечание: В любой момен- времени шинами управляет юлько один микропроцессог адресации памяти, обычно реализуемый в микропроцессорных системах. При ПДП адресацию будет выполнять какая-либо другая система или процессор; это значит, что какой-либо дру-

|