| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

Космонавтика Архитектура 3-х шинных систем НОЙ прог4)аммы, находящейся в памяти гю определенному адресу. Вспомним, что запрос на прерывание может поступить в произвольный момент времени. Это значит, что микропроцес- Поступление запроса иа прерывание I Установка иа выходе INTE состояния логического О \ Подача сигнала подтверждения прерывания INTA \ Подача вектора рестарта иа шину данных микропроцессора 8080 Пересылка адреса возврата в стек I Выполнение программы, указанной вектором рестарта Рис. 6.10. Последовательность действий, выполняемых микропроцессором 8080, сор должен обеспечить быстрое принятие решения, основываясь на состоянии некоторых внутренних флажков. Так как во время выполнения программы обработки прерываний содержимое этих флажков или регистров может быть разрушено, иеоб.хо- PUSH PSW PUSH н PUSH D PUSH в Сохранение состояния регистров Программа обработки прерывания Восстановление состояния регистров POP В POP D POP Н POP PSW EI RET Рис. 6.Г1. Фрагмент программы, иллюстрирующий, как сохраииетси и восстанавливается состояние системы . димо сохранить их состояния. Это можно осуществить посредством записи содержимого регистров в стек сразу после входа в программу обработки прерываний. А потом, непосредственно перед выходом из программы обработки прерываний, нужно будет восстановить их состояния. Рассмотренная идея иллюстрируется программой, представленной на рис. 6.11. Подведем итоги обсуждения вопроса организации прерываний в микропроцессорной системе 8080. Запрос на прерывание поступает от внешних аппаратных средств. Последующие запросы на прерывания могут быть разрешены или запрещены программно. Подачей сигнала шины управления INTA обеспечивается помещение на шину данных вектора прерывания. Вектор прерывания является адресом или указателем, определяющим некоторую точку входа в программу обработки прерываний. Прежде чем приступить к выполнению программы обработки прерывания, начало которой определяется вектором прерывания, в стек помещается адрес возврата. Последнее действие выполняется подобно тому, как это делается при обращении к подпрограмме. Для возвращения в прерванную программу последней в программе обработки прерываний должна выполняться команда RET. 6.3. Прерывания в микропроцессоре 8085 Прерывания в микропроцессоре 8085 могут осуществляться несколькими способами. Один из них полностью совпадает с рассмотренным нами способом организации прерываний в микропроцессоре 8080. Вход микропроцессора 8085, на который по- Рис. 6.12. Схема, демонстрирующая выводы микропроцессора 8085, используемые для подачи запроса на прерывание и для выдачи, сигнала подтверждения.

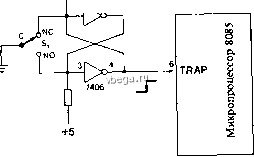

Запрос на прерывание Используется для подачи вектора рестарта на шину данных дается запрос на прерывание, имеет обозначение INTR. Этому входу соответствует вывод 10. Сигнал подтверждения прерывания INTA (вывод 11 микропроцессора 8085) фактически является сигналом разрещения подачи вектора рестарта на шину данных. Упомянутые выводы и соответствующие им сигналы показаны на рис. 6.12. На рисунке показано, что когда подается сигнал подтверждения прерывания INTA, т. е. когда на выводе 11 уровень напряжения понижается, вектор рестарта подается на шину данных и микропроцессор начинает выполнять программу обработки прерывания, соответствующую полученному вектору рестарта. В данном случае векторам рестарта поставлены в соответствие точно такие же адреса памяти, как и в рассмотренной нами системе прерываний для микропроцессора 8080 (см. рис. 6.8). В отличие от микропроцессора 8080 в мик-процессоре 8085 не предусмотрен сигнал INTE. Это означает. ЧТО ДЛЯ выдачи сигнала сброса запроса на прерывание нужно-использовать порт вывода. Согласно схеме, представленной на рис. 6.13, после поступления запроса на прерывание, вырабатываемого триггером типа D (см. схему на рис. 6.2), для сброса запроса на прерывание необходимо подать сигнал на вход Сброс триггера типа D. На рис. 6.13 показана линия сброса D-триггера, началом которой является выход порта вывода. Схема. представленная на рис.6.2 На вход Сброс триггера тнпаО Шипа умр;пле11ия lllmui ллтых Сброс запроса на прерывание Шина адреса Порт вывода Рис. 6.13. Схема формирования сигнала сброса запроса иа прерывание, в ко торой используется специальный порт вывода. Чтобы снять запрос на прерывание, микропроцессор 8085 должен записать определеииое слово данных в порт вывода. В микропроцессоре 8085 также предусмотрен вход TRAP (вывод 6), предназначенный для подачи запросов на прерывание, которые не могут маскироваться. Это значит, что запросы на прерывание, подаваемые на вход TRAP, никогда не могут быть запрещены программно. Запросам на прерывание по входу TRAP присвоен самый высокий приоритет по отношению ко всем другим прерываниям. Если в один и тот же момент времени поступят хотя бы два запроса на прерывание, то запрос прерывания, поступивший на вход TRAP, будет иметь приему-щество над всеми другими. При использовании прерываний по входу TRAP нет необходимости подавать вектор рестарта на шииу данных. Этот вектор рестарта автоматически формируется и выдается микропроцессором 8085. Ему соответствует адрес рестарта 24i6. Для подачи запроса на прерывание на вход TRAP может быть использована схема, показанная на рис. 6.14. Отметим, что в данной схеме отсутствует триггер типа D. Вход TRAP является чувствительным как к фронту, так и к уровню сигнала. Сигнал на входе TRAP должен иметь уровень логической I в течение времени, которое требуется для его ввода в микропроцессор 8085. Однако микропроцессор устанавливает появление сигнала иа этом входе только тогда, когда на нем происходит переход к уровню логического О и обратно к уровню логической 1. Для этого кнопочный переключатель, обозначенный на рнс. 6.14 через Si, нужно наж ать и отпустить.  4,7 кОм Рис. 6.14. Схема формирования сигнала прерывания TRAP в микропроцессоре 8085. В микропроцессоре 8085 предусмотрено еще три входа для подачи запросов на прерывания. Эти входы имеют следующие обозначения: RST 7.5, RST 6.5, RST 5.5. Им соответствуют выводы 7, 8 и 9 микропроцессора 8085. При поступлении запросов на прерывание .иа указанные входы нет необходимости обеспечивать подачу адресов рестарта на шину данных - мнкропро-Вход прерывания Адрес памяти 5.5 2Ci. 6.5 34 7.5 ЗСи Вектор рестарта Адрес памяти 5 28i, 6 30м 7 38i. Рис. 6.15. Адреса памяти векторов рестарта. Отметим, что адрес вектора рестарта 6.5 расположен между адресами векторов рестарта RST 6 и RST 7. цессор определяет их автоматически. Адреса для векторов рестарта даны на рис. 6.15. Отметим, что адреса векторов прерываний 5.5, 6.5 и 7.5 физически расположены между векторами рестарта. В микропроцессоре 8085 сигналы рестарта 5,5 и 6.5 имеют такие же временные характеристики, как и сигнал прерывания INTR. Сигнал RST 7.5 имеет некоторые отличия. Сигнал RST 7.5 является активным, нарастающим, чувствительным к фронту запросом на прерывание. Для осуществления запроса на прерывание требуется подать единственный импульс. Это означает, что запрос на прерывание RST 7.5 производится просто подачей импульса на вывод RST 7.5 микропроцессора 8085. Этот импульсный сигнал будет запоминаться до тех пор, пока запрос на прерывание система не обработает или не сбросит.  Импульс запроса на прерывание RST 7,5 Рнс. 6.16. Временная диаграмма сигнала запроса на прерывание RST 7.5. Временная диаграмма, представленная на рис. 6.16, иллюстрирует некоторые особенности сигнала RST 7.5. Наряду с отличиями в аппаратных средствах, используемых для организации прерываний в микропроцессорах 8080 и 8085, имеются также отличия и в соответствующем программном обеспечении. Основное отличие обусловлено тем, что в системе команд микропроцессора 8085 есть команды установка маски прерываний (SIM). С помощью этой команды могут быть разблокированы только определенные линии запросов на прерывания. Это зна чит, что прерывания RST 5,5, RST 6.5 и RST 7.5 могут блокироваться так же, как запрос прерывания INTR. Единственным запросом на прерывание, который нельзя блокировать программно, является запрос на прерывание TRAP. Прерывание по входу TRAP не может маскироваться и будет обрабатываться всегда. MVI А, 18I-I Рнс. 6.17. Фрагмент программы для микропроцессора 8085, обеспечивающий установку маски прерываний. Код 18,6 определяет, что 4-му и 3-му разряду маски прерываний присваивается значение 1. На рис. 6.17 представлен небольшой фрагмент программы для микропроцессора 8085, демонстрирующий применение команды установки маски прерываний SIM. Этот фрагмент обычно используют в начале программы и, кроме того, при обработке запросов на прерывания. Назначение разрядов маски прерываний описано в руководстве по программному обеспечению системы 80Й5. .4. ЦП Z80 имеет два входа, предназначенные для приема запросов иа прерывание: запрос на прерывание (INT, вывод 16) и запрос на немаскируемое прерывание (NMI, вывод 17). Сигнал запроса на прерывание INT является маскируемым, т. е. это прерывание может программным путем разрешаться или запрещаться. Немаскируемое прерывание будет восприниматься ЦП Z80 все время. Немаскируемое прерывание имеет вектор рестарта, равный 66ie. Это значит, что, когда произойдет Рис. 6.18. Схема подачи запроса иа прерывание и формирования сигнала подтверждения прерывания в микропроцессоре Z80. Микропроцессор Z80 INTERRUPT REQUEST Схема, представленная на рнс. 6.2 iorq Сигнал Сброс из порта ввода-вывода 74LS32 -Сигнал INTA, используемый для разрешения полачи вектора рестарта иа шину данных немаскируемое прерывание, ЦП начнет выполнение той программы обработки прерывания, первая команда которой находится по адресу 66ie. В микропроцессоре Z80 предусмотрено три различных способа обработки запросов на прерывания, поступающих на вход маскируемых прерываний, т. е. на вывод 16. Первый способ аналогичен реализованному в микропроцессоре 8080. Когда происходит прерывание, один из векторов рестарта RSTo- RST7 помещается на шину данных. Схема, иллюстрирующая описанные действия, приведена на рис. 6.18. Замети, что для формирования сигнала INTA используются сигналы Mi и IORQ, вырабатываемые ЦП Z80. Сброс запроса на прерывание в данном случае выполняется так же, как и в микропроцессоре 8085. Для этого может быть использован особый порт вывода. Когда выполняется установка начального состояния микропроцессора Z80, сбрасывается и вход запрос на прерывание (вывод 16). Подтверждение поступления запроса на прерывание осуществляется способом, рассмотренным нами выше. Второй способ реакции ЦП Z80 на прерывание состоит в следующем. Программным путем система может быть подготовлена к обработке прерывания так, что, когда аппаратные средства инициируют запрос на прерывание, автоматически бу- Прерьшания в микропроцессоре Z80

|