| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

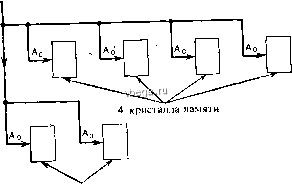

Космонавтика Архитектура 3-х шинных систем €м С устройства ввода. В течение промежутка времени, пока на шине управления сохраняется этот сигнал, данные с устройства ввода передаются на шину данных. Сравнивая рассмотренные до сих пор временные диаграммы, можно заметить, что синхронизация процессов при чтении данных из памяти и с устройства ввода схожа. То же самое относится и к синхронизации процессов при записи данных в память и на устройство вывода. Как уже упоминалось, с помощью большинства микропроцерсоров можно строить системы, в которых нет различия между записью данных в память и на устройство вывода либо чтением данных из памяти и с устройства ввода. 1.10. Операции с внутренними регистрами Операции с внутренними регистрами представляют собой пятую функцию из ряда основных, реализуемых микропроцессорной системой. Примером такой операции может служить операция ADD, по которой содержимое внутреннего регистра микропроцессора складывается с содержимым аккумулятора. Для разных микропроцессоров существуют особенности выполнения этой операции, однако при этом все необходимые действия реализуются внутри единственного кристалла микропроцессора, так что внешние шины системы не используются. В начале нашего обсуждения мы установили,- что пять перечисленных функций микропроцессора позволят начинающему читателю адекватным образомописать большинствопроцессов в микропроцессорной системе. Позднее мы обсудим некоторые дополнительные функции, а пока основное внимание будет сосредоточено на пяти указанных, которые постоянно использу-, ются вне зависимости от сложности программного обеспечения системы. В качестве примера рассмотрим в общем виде выполнение команд в микропроцессорной системе. После этого станет очевидной периодическая повторяемость пяти основнызс функций. 1.11. Выполнение команд в системе с 3 шинами Основная последовательность действий при выполнении любой команды такова: 1. Микропроцессор выдает в память адрес, по которому хранится код операции команды. 2. Код операции читается из памяти и вводится в микропроцессор (функция 2). 3. Команда дешифрируется микропроцессором. 4. Микропроцессор настраивается на выполнение одной из пяти основных функций в соответствии с результатами дешифрирования считанного кода операции. 5. Предположим, что была считана команда с непосредственными данными. По этой команде в один из внутренних регистров микропроцессора загружается константа. Микропроцессор настраивается на чтение второго байта данных из памяти. 6. Второй байт данных из памяти загружается во внутренний регистр микропроцессора (функция 5). Главное здесь заключается, в том , что вне зависимости от кода операции микропроцессор настраивается на выполнение одной из пяти рассмотренных выше функций. Снова подчеркнем, что существуют и другие реализуемые системой функции, например прерывание, прямой доступ к памяти (ПДП), ожидание. Эти функции будут обсуждаться в последующих главах. Однако вполне возможно спроектировать управляемую микропроцессором систему, в которой не используются никакие дополнительные функции, за исключением пяти приведенных выше. Позднее рассмотрим проектирование таких систем. Однако чтобы не оказаться во власти заблуждения, следует помнить, что приведенный здесь подход к проектированию имеет не только методологическое значение и оказывается весьма эффективным при настройке, проектировании и отладке многих систем, управляемых микропроцессорами. 1.12. Управление синхронизацией системы При изучении различных временных соотношений, соблюдение которых необходимо для реализации пяти основных функций, возникает естественный вопрос: каким образом осуществлять правильную синхронизацию всех сигналов? Фундаментальная особенность использования микропроцессоров при проектировании систем заключается в следующем: синхронизация всех сигналов в системе осуществляется схемами, входящими в состав кристалла микропроцессора. При дзбработке микропроцессором программной команды чтения из памяти выработка и синхронизация необходимых сигналов для формирования адреса, для выборки данных и для управления осуществляются самим микропроцессором. Пользователи микропроцессора должны знать синхронизацию всех его сигналов. Это способствует правильному использованию временных соотношений при проектировании системы. Такой несколько упрощенный .подход позволяет достаточно точно представить функционирование большого числа существующих микропроцессоров. В дальнейшем этот подход будет использован при проектировании микропроцессорных систем на базе устройств 8080, 8085, Z80. 6800. 1.13. Выводы В настоящей главе была рассмотрена архитектура типичной мийропроцессорной системы с 3 шинами. Эти три шины включают: адресную шину; шину данных; шину управления. При реализации общих системных функций было также показано взаимодействие сигналов различного уровня, подавае-мых на эти шины. К этим функциям относятся: 1. Запись данных в память системы. . 2. Чтение данных из памяти системы. 3. Запись данных в устройство вывода системы. 4. Чтение данных с устройства ввода системы. 5. Выполнение операций с внутренними регистрами. Было показано, каким образом эти основные функции реализуются в системе с 3 шинами. Основные положения настоящей главы применимы к весьма широкому кругу микропроцессорных систем. В, последующих главах эти общие положения будут использованы при построении реальных микропроцессорных систем. В гл. 2 определяется архитектура систем с 3 шинами на базе существующих схем микропроцессоров 8080, 8085, Z80 и 6800. В проектируемых устройствах рассматриваемые в главе общие положения приобретают практический смысл. В настоящей главе будет рассмотрено, каким образом архитектура систем с 3 шинами может быть реализована с использованием реальных микропроцессоров. Одновременно будут обсуждаться микропроцессоры 8080, 8085, Z80 и 6800, для каждого из которых будут спроектированы шины адресная, данных и управления. В процессе проектирования этих шин будут рассмотрены особенности реализации шин для каждого микропроцессора. В главе приводятся реальные схемы. Они могут быть использованы в качестве центрального процессора (ЦП), построенного на любом из рассматриваемых микропроцессоров. После построения шин будут обсуждены вопросы интегрирования памяти, устройств ввода и вывода в рамках одной микропроцессорной системы. Эти вопросы поднимаются в настоящей и последующих главах. 2.1. Пояснения к адресной шине системы При проектировании адресной шины прежде всего оценивают величину токовой нагрузки, при которой каждая адресная шина работает удовлетворительно. Адресные линии в микропроцессорной системе связаны cq множеством адресных входов, подключенных параллельно, как это показано на рис. 2.1. Если для адресной линии характе1ен ток, по величине превосходящий допустимое значение на выходе микропроцессора, то такую линию необходимо буферировать. Под буферированием понимают такую процедуру, при которой адресная линия снабжается средствами съема избыточ- ~ ного тока. Например, предположим, что адресные линии микропроцессорной системы должны управлять адресными входами четырех блоков памяти и двух портов ввода-вывода, что показано на рис. 2.2. Не будем обсуждать правомерность приверженных в схеме соединений. Этот вопрос раскрывается в гл. 3. Просто допустим, что приведенные соединения возможны. Величина тока в адресной линии, управляющей блоками памяти и устройствами ввода-вывода, равна сумме входных токов всех четырех блоков памяти и двух портов ввода-вывода. Пусть ПОСТРОЕНИЕ СИСТЕМ С 3 ШИНАМИ НА БАЗЕ УСТРОЙСТВ 8080, 8085, Z80 и 6800 в качестве памяти используется оперативное запоминающее устройство (ОЗУ) 1024X4 бит типа 2114. По техническим характеристикам устро11Ства 2114 видно, что нагрузка каждого входа равна 10 мкА и не зависит от логичес* кого состояния адресной линии. Это означает, что общая на грузка от микропроцессора на адресной линии при работе с па-мятью есть 4X10 или 40 мкА. Микропроцессор + 5 в- Адресная шина

Рис. 2.1. Подсоединение к адресной шине микропроцессора нескольких устройств (нагрузок). На схеме показаны четыре нагрузки. Далее допустим, что при построении входных портов рис. 2.2 используются устройства 74LS (маломощные устройства Шот-тки). Это означает, что каждое устройство вывода системы создает на адресной линии нагрузку, соответствующую стандартной для 74LS. Согласно техническим характеристикам 74LS, эта нагрузка равна 20 мкА при сигнале логической 1 и 0,4 мА- при логическом 0. В табл. 2.1 приведены значения суммарной нагрузки на адресной линии системы, показанной на рис. 2.2. Из табл. 2.1 видно, что максимальная нагрузка на адресной линии для состояния логической 1 равна 80 мкА, а для состояния логического О-840 мкА. Таблица 2J Примерная нагрузка для адресной линии Ао (рнс. 2.2) Тип памяти 2114 Тип устройства ввода-вывода 74LSXX Нагрузка (мкА) Для одного блока 10 мкА (логическая 1) 10 мкА (логический 0) Для каждого устройства 400 мкА (логический 0) 20 мкА (логическая 1) Общая нагрузка 40 мкА+800 мкА=840 мкА (логический 0) 40 мкА+ 40мкА= 80мкА (логическая I) Для всей памяти / 40 мкА (логическая 1) 40 мкА (логический 0) Для всех устройств 800 мкА (логический 0) 40 мкА (логическая 1>  2 порта ввод а-вывод а Рис. 2.2. Использование адресной линии Ао, исходящей из микропроцессора, для управления четырьмя линиями памяти и двумя портами Езода-выиода (заземление на схеме ие показано). Микропроцессорная система  Длинный кабель  Устройство ввода-вывода, ; например, построчно печатающее устройство Рис 2.3. Микропроцессорная система может использоваться с устройством вывода типа построчно печатающего устройства, которое может соединяться с системой посредством длинного кабеля. Такой кабель обладает большой емкостью, поэтому для передачи по нему сигнала необходимо использовать специальные схемы.

|

||||||||||||||