| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

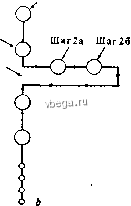

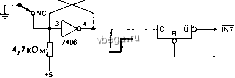

Космонавтика Архитектура 3-х шинных систем В настоящей главе рассматриваются вопросы организации прерываний, режима ожидания и режима прямого доступа к памяти в микропроцессорах 8080, 8085, 6800 и Z80. Сначала обсудим каждый из указанных вопросов, а затем рассмотрим методы реализации аппаратных средств, применяемых для обеспечения этих режимов в обсуждаемых микропроцессорах. Будем также рассматривать некоторые специальные команды и принципы построения программного обеспечения, используемые для осуществления трех указанных режимов. Изложение вопросов программного и аппаратного обеспечения прерываний, режима ожидания н режима прямого доступа к памяти будет носить основополагающий характер. Разобравщись, как реализуются эти режимы в простых микропроцессорных системах, будет легко адаптировать их к микропроцессорным системам с более сложной архитектурой. По каждому из трех рассматриваемых режимов изложение будет проводиться в следующей последовательности. Мы будем описывать основные идеи программного и аппаратного обеспечения рассматриваемых режимов н демонстрировать примеры их реализации в распространенных типах микропроцессорных систем. Затем будем рассматривать особенности реализации указанных режимов в каждом из четырех обсуждаемых нами микропроцессоров. Принципы реализации сравниваются между собой. Изучив материалы настоящей главы, вы сможете использовать микропроцессорные системы, в архитектуре которых реализованы рассмотренные здесь режимы. 6.1. Основные представления о прерываниях Сначала дадим общие представления о том, что такое прерывание. В рассматриваемых нами системах микропроцессор действовал как системный контроллер, т. е. он всегда выполнял команды программы в том порядке, в котором они были расположены в памяти. Это значит, что никакое вмешательство пользователя не могло воздействовать на ход выполнения программы, по которой уже начал работать процессор. Система прерываний позволяет изменять ход выполнения программы на ос- Шаг 1 Шаг 1 Шаг 2 Произошло прерывание Шаг 3 Шаг 4  Рис. 6.1. Схема последовательного выполиеиия четырех шагов программы (я); схема, демонстрирующая появление запроса иа прерывание после выполнения 1-го и 2-го шагов программы (б). Вследствие прерывания последовательное выполнение программы прекращается до тех пор, пока не выполнятся шаги 2а и 26. После выполиеиия этих шагов продолжается нормальное выг полиение прерванной программы. Затем в микропроцессор поступает сигнал прерывания. После наступления прерывания выполнение программы прекращается и управление передается другой программной секции. Как толь ко работа этой программной секции завершится, будет осуществлен переход к прерванной программе и продолжится ее нормальное выполнение. На рис. 6.1,6 показано, что, когда появляется сигнал прерывания, нормальный ход программы нарушается. Прерывание происходит между 2-м и 3-м шагами программы. Однако оно могло произойти и между другими шагами. Вообще, сигнал прерывания, поступающий в микропроцессор, является асинхронным, а это значит, что он может прийти на любом этапе работы программы. В рассматриваемом примере прерывание программы могло бы произойти и между шагами 3 и 4. Для системы не имеет значения, когда оно наступает, так как обработка прерываний всегда одинакова. В литературе по микропроцессорам такой принцип обработки прерываний называется прерывание по вектору. ПРЕРЫВАНИЯ, РЕЖИМ ОЖИДАНИЯ И РЕЖИМ ПРЯМОГО ДОСТУПА К ПАМЯТИ В МИКРОПРОЦЕССОРАХ 8080, 8085, 6800 и Z80 ковании сигналов, поступающих в микропроцессор. Рис. 6.1 дает наглядное представление о возникновении прерывания программы. Рис. 6.1, а соответствует случаю непрерывного последовательного выполнения четырех шагов программы. Рнс. 6.1,5 показывает, что первые два шага программы выполняются так же, как и при непрерывном последовательном ее выполнении. В данном случае понятие вектор разнозначно понятию указателя. Этот вектор показывает микропроцессору, какой адрес нужно использовать, чтобы вызвать соответствующую программу обработки прерывания в момент его Возникновения. Таким образом, понятие вектор здесь означает лишь только адрес памяти. Понятие прерывание по вектору означает, что в системе будут происходить прерывания, а вектор-это адрес начала программы обработки прерываний. И если мы определим прерывание как вынужденный переход микропроцессора на выполнение определенной программы в момент поступления сигнала прерывания-это будет вполне оправдано. Значит, независимо от того, какую программную секцию выполняет микропроцессор, при наступлении прерывания он начнет выполнять другую программную секцию, после выполнения которой вернется к прерванной задаче. В некоторых микропроцессорах и, в частности, в каждом из четырех микропроцессоров, рассматриваемых нами, используются два типа прерываний: 1) не маскируемые прерывания и 2) маскируемые прерывания. Если прерывание не маскировано, то микропроцессор будет реагировать на поступление соответствующего сигнала прерывания. Всякий раз, когда во время выполнения программы наступает немаскированное прерывание, микропроцессор должен среагировать на него. Принцип маскирования прерываний состоит в том, что реакция микропроцессора на сигналы прерывания может быть разрешена или запрещена программным путем. Маскируемые прерывания могут эффективно отключаться программными средствами. Мы не будем обсуждать многочисленные вопросы, связанные с применением маскируемых и -немаскируемых прерываний в микропроцессорных системах. Мы лишь покажем, как прерывания этих типов реализуются в каждом из четырех рассматриваемых микропроцессоров. Начнем с изучения системы прерываний для микропроцессора 8080. 6.2. Прерывания в микропроцессоре 8080 Для Осуществления прерываний могут использоваться различные аппаратные средства, в частности схема, показанная на рис. 6.2. С помощью этой схемы сигнал прерывания может быть яодан на любой из рассматриваемых нами микропроцессоров. Рассмотрев эту схему, мы сможем понять, как каждый процессор реагирует на запрос прерывания, поступающий от внешних аппаратных средств. Микропроцессор определенным образом связывается со схемой, представленной на рис. 6.2. На данном рисунке эта связь показана стрелкой, идущей от микропроцессора на вход сброса триггера 74LS74. Прерываниз* режим ожидания и прямой доступ к памяти 173 \ I - II... Кратко изложим йринцип действия схемы, представленной на рис. 6.2. Слева на рисунке изображена схема, устраняющая влияние эффекта дребезжания ключа. Она состоит из двух инверторов с открытым коллектором и однополюсного двухходового кнопочного переключателя. Когда ключ Si находится в состоянии покоя (NC), его центральный вывод соединен с нормально замкнутым полюсом. Нор- ♦в 4,7 кОм !4,7кОм

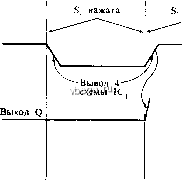

74LS74 К микропроцессору  Из микропроцессора 1* Рис. 6.2. Схема устройства, вырабатывающего сигнал прерывания микропроцессора. мально замкнутый полюс соединяется с выводом 3 схемы IC На этом выводе будет уровень логического 0. Вывод 4 схемы ICi будет находиться в состоянии логической 1., На входе синхроимпульсы триггера 74LS74 также будет установлен уровень логической 1. Схема 74LS74 представляет собой триггер, запускаемый фронтом импульса. Когда на входе синхроимпульсы схемы 74LS74 происходит переход от уровня логического О к уровню логической 1, данные со входа D будут переданы на выходы Q и Q. Исходя из рис. 6.2, можно предположить, что когда ключ находится в нормальном положении, иа входе синхронизация триггера 74LS74 должен быть уровень логической 1. Если нажать кнопку Si, то центральный вывод Si соединится с нормально разомкнутым выводом переключателя. При этом установится уровень логического О иа выводе I схемы ICi и уровень логической 1 на выводе 2 этой схемы. Следовательно, когда кнопка Si нажата, на входе синхроимпульсы схемы 74LS74 установится состояние логического 0. При этом состояние триггера не изменится. Если теперь отпустить кнопку Si, то на входе синхроимпульсы схемы 74LS74 произойдет переход от состояния логического О к состоянию логической 1. Таким образом, посредством кратковременного нажатия кнопки Si обеспечивается передача данных со входа D на выходы Q и Q. Временная диаграм- ма этого процесса представлена на рис./.З. На вход D и вход установки триггера, которым в схеме 4LS74 соответствуют выводы 2 и 4, через резистор с сопротивлением 4,7 кОм подается напряжение +5 В. Таким образом на входах D и S триггера 74LS74 всегда поддерживается уровень логической 1. Данные передаются во время нарастания переднего фронта импульса на входе синхроимпульсы : выход Q всегда переходит в состояние логической 1, а выход Q -в состояние логического 0. Так формируется сигнал прерывания микропроцессора. в нормальном пдложении  отпущена Данные со входа D схемы 74LS74 передаются на ее выходы Q н Q Рис. 6.3. Временнйя диаграмма сигнала на выходе Q, определяемого положением кнопки Si. Когда кнопка отпускается, на выходе Q устанавливается состояние логической 1, а на выходе Q -состояние логического 0. После поступления сигнала прерывания микропроцессор должен в ответ послать сигнал, имеющий логическое значение О, на вход сброс триггера 74LS74. Это обеспечит переход выхода Q в состояние логического О, а выхода Q -в состояние логической 1. Так микропроцессор выполняет сброс запроса прерывания, выработанного внещними аппаратными средствами. Используя рассмотренную схему, можно формировать и асинхронно подавать на определенные входы микропроцессора сигналы прерывания. Микропроцессор может выполнять программу, а мы, нажимая в некоторый момент времени на кнопку §1, посылаем сигнал прерывания. Когда будут рассматриваться специфические вопросы обработки прерываний в микропроцессорах, мы снова обратимся к схеме, представленной на рис. 6.2, чтобы более подробно разобраться в том, почему для генерации запроса на прерывание необходимо использовать триггер. (Сейчас этот вопрос рассматривать преждевременно. В нем будет легче разобраться после подробного рассмотрения системы прерываний в микропроцессоре 8080.) СО чо ? ё = б Is Выход Q схемы-74LS74 Вход Сброс IMTF схемы 74LS74 16 I Рис. 6.4. Блочная схема подключения формирователя сигнала прерывания, схема которого дана на рис. 6.2, к микропроцессору 8080. 1. Вход INT (вывод 14 микропроцессора 8080) перешел в состояние логической 1. Это означает, что прерывание запрашивается внешними аппаратными средствами. 2. Микропроцессор 8080 принял запрос на прерывание, поступивший на вывод 14, на выходе ШТЕ (вывод 16) будет установлен уровень-логического 0. Эти два события являются основными в рассматриваемом интерфейсе. Однако имеются и другие аппаратные средства, используемые в микропроцессоре 8080 для обработки прерываний. Пока мы только рассмотрели, как образуются запросы на прерывания и как выполняется сброс запроса на прерывание. Когда вывод 16 микропроцессора 8080 находится в состоянии логической 1, микропроцессор находится в режиме приема запроса на прерывание от внешнего оборудования. Если на выходе ШТЕ (вывод 16) устанавливается состояние логического О, микропроцессор игнорирует все запросы на прерывания, поступающие на вход ШТ (вывод 14). В микропроцессоре 8080 используются только маскируемые прерывания. В системе команд микропроцессора 8080 есть две специальные команды: команда запрещения прерываний DI и команда разрешения прерываний EI. С помощью этих двух команд можно изменять состояние выхода ШТЕ. Например, когда выполняется начальная установка микропроцессора ,8Ш0, выход ШТЕ переводится в состояние логического 0. Это значит, что непосредственно после установки начального состояния микро- На рис. 6.4 показансхема подключения аппаратных средств, обеспечивающих формирование запроса на прерывание (см. рис. 6.2), к микропроцесру 8080. Этот интерфейс, очевидно, очень прост. Линия, по кЬ;орой в микропроцессор поступает -запрос на прерывание, имеет* обозначение ШТ. Она подводится к выводу 14 микропроцессора 8080. Этот микропроцессор имеет специальный выход ШТЕ (вывод 16), который используется для подачи сигнала на вход Сброс схемы 74LS74. В процессе обработки прерывания, запрос на которое уже, предположим, поступил, можно выделить следующие два этапа:

|

||||||||||||||