| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

Космонавтика Архитектура 3-х шинных систем ЮкОм SPST ~рмкф Схема отключения питания

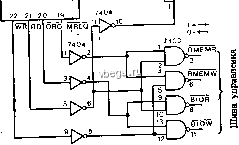

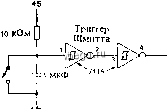

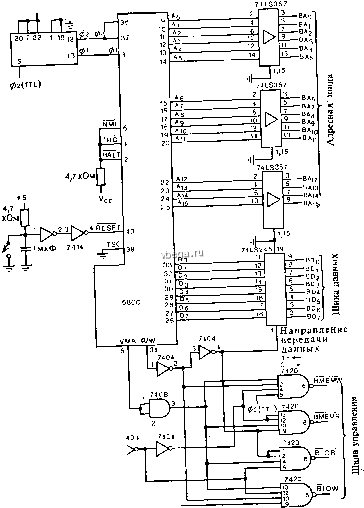

8085 lO/M WR RD AD, AD AD AD, AD; AD; AD, AD, , 7404 7404 5l\6 7404 74LS04 7404 Запрос ввода-вывода =1 Запрос памяти = i 74LS367 1, 15 -BA -ВА -BA,. -BA,: -BA -BA 1, 15 74LS367 -BAg -BAe 74LS374 BA, BAe BA BA, -ВАз -BA, -BA, -BA 19 18 74LS245 -BD, -bd, -BD, -BD3 -BO, -BO, B0 740O Направление передачи данных О = -f- > > -BIOR -Blow BMEMR BMEMW Рис. 3.27. Схема использования микропроцессора 8085 в качестве контроллера системы. юкОм Слюч /Г ==1 1 мкФ Триггер Шмитта 7414 На вход Сброс микропроцессора Z80 Ряс. 3.28. Схема отключения питания микропроцессора Z80.  4,7 кОм В1 SHQ ШГ 5,1 кОм If :1мкФ 7414

7413367 ВА, ВА BA2 ВАЗ BA4 ВАб 1,15 74LS367 3 ВАб ВА, ВА8 ВАэ

.LS245] Э

-BA,j -ВА,з -BAi4 -ВА,5 1,15 19 -BDo J2 BDJ !4-BD4 B05 :i-bd; Направление передачи данных  Рис. 3.29. Схема использования микропроцессора Z80 в качестве контроллера системы. предназначенной для микропроцессоров 8080 и 8085. Как и в случае указанных микропроцессоров, Z80 после установки в начальное состояние начинает выполнять программу с команды, находящейся по адресу 0000. На рис. 3.29 представлена полная схема микропроцессорной системы Z80, спроектированной для работы в качестве системного контроллера. 3.18. Подготовка микропроцессора 6800 дпя работы режиме системного контроллера Теперь сосредоточим внимание на некоторых особенностях схемы включения микропроцессора 6800 в качестве системного контроллера.. На вход HALT (вывод 2) подадим уровень, соответствующий логическому значению 1. Это предотвратит возможность выполнения операции прямого доступа в память. Обеспечим также уровень логической 1 на выводах 4 и 6, на которые подаются входные сигналы IRQ и NMI. Благодаря этому в микропроцессоре 6800 не будут возникать прерывания. В микропроцессоре 6800 не могут возникать паузы во время нормального выполнения программы. Это достигается благодаря растягиванию сигналов генератора тактовых импульсов. Более подробно рассмотрим этот вопрос в гл. 6. Подадим также вторую фазу тактовых импульсов на вход DBE (сигнал отпирания шины данных). Когда в последовательности фаза 2 появляется уровень логической 1, шина данных обеспечивает передачу данных в микропроцессорной системе. 3.19. Начальная установка микропроцессора 6800 Схема начальной установки микропроцессора Z80, рассмотренная нами выше, может использоваться и для начальной установки микропроцессора 6800. В этом случае она выглядит, как показано на рис. 3.30. Напомним, что после выполнения начальной установки микропроцессор 6800 не начинает выполнение программы с ячейки, имеющей адрес 0000. После выполнения начальной установки микропроцессор подает на адресную шину адреса FFFE и FFFF. Содержимое ячейки с адресом FFFE представляет собой младшие восемь разрядов формируемого адреса. По адресу FFFF находятся восемь старших разрядов формируемого адреса, которые рассматриваются микропроцессором как некоторые данные. Полный 16-разрядный адрес получается из слов, содержащихся в указанных ячейках. Таким образом, ячейки памяти FFFE и FFFF содержат фактический адрес, с которого начинается выполнение программы после начальной установки микропроцессора 6800. Ключ  На вход RESET (вывод 40микропроцессора 6800) Рис. 3.30. Схема отключения питания микропроцессора 6800. о BE

4г 74LS4 2 02(TTL) Риа 3.31. Схема использования микропроцессора 6800 в качестве коитрол- лера системы. Эта особенность микропроцессора 6800 обыкновенно используется для адресации в область старших адресов имеющегося в распоряжении адресного пространства ПЗУ (64К). Теперь ясно, что в ПЗУ должен находиться адрес, который должен при запуске микропроцессора разместиться на шине- данных. Рассмотрим пример. Предположим, что в ячейке памяти с адресом FFFE содержится код 63, а в ячейке памяти с адресом FFFF- код 7F. Таким образом, когда микропроцессор устанавливается в начальное состояние, программа восстановления системы начнет свое выполнение с адреса 7F63, тогда как другие микропроцессоры после сброса начинают работать по программе, выбирая первую команду из ячейки с адресом 0000. Полная структурная схема микропроцессора 6800, используемого в качестве системного контроллера, представлена на рис. 3.31. 3.20. Выводы В этой главе были рассмотрены некоторые детали реализации микропроцессорных систем с 3 шинами, построенных на микропроцессорах 6800, 8080, 8085 и Z80. Были показаны способы подключения ПЗУ и ОЗУ к микропроцессорам указанных типов. Наконец, были представлены полные системные проекты применения каждого из четырех типов микропроцессоров в качестве контроллеров микропроцессорных систем. В оставшейся части книги будут рассмотрены некоторые другие особенности микропроцессорных систем и вопросы усовершенствования изученных нами типовых вариантов построения систем. Однако первый шаг уже сделан. Важно понимать принцип построения типовых вариантов микропроцессорных систем, прежде чем приниматься за изучение более сложных дополнительных схем и возможностей. Рассмотренное по существу является скелетом системы. Однако не следует впадать в заблуждение и считать такую систему бесполезной. В действительности справедливо обратное. Дело в том, что системы, построенные на основе таких скелетов, используются повсеместно. Иногда забывают, что для того чтобы оправдать применение микропроцессора в проекте системы, нет необходимости использовать все его возможности. Также иногда забывают, что используемые системы не нуждаются в приукрашивании. В настоящее время микропроцессор является очень дешевым устройством и в большинстве случаев делается по совершенно простому схемному проекту. Нет необходимости быть высококвалифицированным проектировщиком систем или инженером-проектировщиком, чтобы проектировать и эксплуатировать микропроцессорные системы. Впервые приступая к проектированию микропроцессорной системы, испыты- ваешь естественную тревогу. В-следующих главах будут продемонстрированы методы дальнейшего развития исходной типовой микропроцессорной системы. Эти методы могут быть предложены лицам, которые работают в режиме экономии и которые не имеют тысяч долларов для расхода на разработку оборудования. Рассматриваемые нами методы будут интересны для лиц, которые заняты кустарной разработкой проекта микропроцессорной системы, и для специалистов, работающих в промышленности. В дальнейшем мы предполагаем обсудить фазу проектирования небольшой системы и фактическое прохождение всех этапов проектирования систем микропроцессорного управления. Конечно, чтобы успешно решить пocтaвлeннyjo задачу, необходимо иметь ясное представление о том, как микропроцессор связывается с другим оборудованием системы. Эта глава содержала начальные сведения; каждая следующая глава, по мере того как наши знания и понимание будут расти, будет раскрывать дополнительные подробности. Усвоив материал, содержащийся в этой главе, и рассмотрев детали, относящиеся к частным системам, представленным в следующей главе, мы добьемся твердого понимания основ. Таким образом, в указанных главах будет представлена информация, которой необходимо овладеть, прежде чем изучать вопросы практического использования микропроцессоров, действующих в реальной обстановке. На протяжении этой книги для пояснения принципов организации микропроцессорных систем используются схемы устройств, наряду с которыми часто приводятся и их полные структурные схемы. Мы нигде не полагаемся на воображение читателей.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||