| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

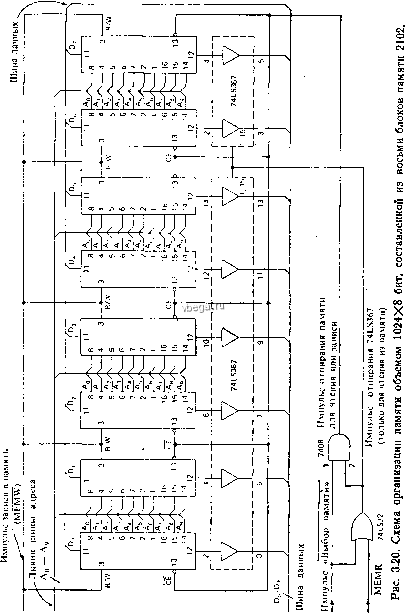

Космонавтика Архитектура 3-х шинных систем реходит в состояние высокого сопротивления), когда выводы 1 и 15 находятся в состоянии логической 1. Когда микропроцессор записывает данные в ОЗУ типа 2102, на выводы 1 и 15 бу- Шина данных микропроцессорной системы WE= о/ (активный уровень)

С шины управления микропроиес - ЧТЕНИЕ=0 сорной системы ЗАПИСЬ=1 Рис. 3.16. Фрагмент схемы, обеспечивающий отключение выходов ОЗУ типа 2102 с помощью схем с тремя устойчивыми состояниями типа 74LS367. фера с тремя состояниями подается сигнал уровня, соответствующего логическому значению 1. Во время выполнения микропроцессором любой операции записи данных в память 2102 внешние аппаратные средства должны обеспечить на указанных выводах состояние логической 1. В течение операции записи микропроцессор будет выводить данные на системную шину данных. Перед этим микропроцессор через шину управления подает сигнал разрешения записи в память. Выход устройства 2102 на время выполнения операции запири с помощью буфера с тремя состояниями отключается от шины данных. Это необходимо для устранения возможности конфликта на шине данных. Отметим, что некоторые полупроводниковые устройства памяти с раздельными входом и выходом сами имеют буферные схемы, предназначенные для отключения их выходов от шины данных в течение операции записи в память. При использовании устройств памяти такого типа достаточно соединить входной и выходной вывод устройства памяти и затем подключить их к шине данных. 3.9. Чтение данных из ОЗУ При выполнении операции чтения данных из ОЗУ состояния линий шины данных определяются сигналами на выходах памяти. Линии данных микропроцессора должны находиться в режиме ввода данных. Вход ОЗУ не будет воздействовать на состояние Шина управления Линия импульса К выходам 1,13 схемы 74LS367 MEMR . Вывод разрешен в состоянии логического () Линия выбора памяти Рнс. 3.17. Схема формирования сигнала, подаваемого на выводы 1 и 15 устройства 74LS367 и обеспечивающего отпирание вь1ходов блоков ОЗУ 2102. шины данных. Это объясняется тем, что сигналы на вход ОЗУ поступают от другого источника. Принципы функционирования ОЗУ в этом режиме почти совпадают с рассмотренными нами выше принципами действия ПЗУ. Для формирования сигнала выбора кристалла, подаваемого на соответствующий вывод ОЗУ, линия выбора памяти и линия шины управления подключаются в соответствии со схемой, показанной на рис. 3.17. В течение времени чтение данных из ОЗУ на линии разрешения записи в ОЗУ 2102 (вывод 3) должен действовать сигнал с логическим значением 1.-Когда модуль ОЗУ 2102 выбран в соответствии с кодом адреса, установленным на шине адреса, а шина управления активизирует линию записи в память, буфер с тремя состояниями открывается сигналом, подаваемым на выводы 1 и 15. Когда буфер с тремя состояниями открыт, данные из ОЗУ 2102 поступают на шину данных. На стадии чтения данных выход блока 2102 связан с соответствующей линией шины данных. После того как микропроцессор выведет данные из ОЗУ 2102, линия чтения из памяти в системной шине управления переводится в нерабочее состояние, а буфер с тремя состояниями 74LS367 переводится в состояние высокого сопротивления. Таким образом будет осуществляться передача данных с щины данных в ОЗУ. Как видим, операция чтения данных из ОЗУ не отличается от операции чтения данных из системного ПЗУ. 3.10. Запись данных в ОЗУ Теперь рассмотрим порядок выполнения операции записи данных в память. Чтобы записать данные в устройство памяти типа 2102, необходимо выполнить следующие действия: 1. Подать на адресные линии адрес памяти. 2. Подать* данные на линии ввода данных ОЗУ. 3. На линию разрещения записи в память подать сигнал, устанавливающий на линии низкий уровень напряжения. Итак, адрес будет подан на щину адреса микропроцессорной системы; линия выбора памяти будет активизирована после дешифрирования кода адреса на адресной щине; микропроцессор будет выдавать информацию на шину данных. Данные готовы для ввода в память. Однако ОЗУ на этой стадии не готово к выполнению, операции, так как на линию выбора кристалла не подан соответствующий сигнал. Чтобы записать данные в память, необходимо ее открыть. Но отпирание памяти фактически заключается в отпирании выходов памяти. Это обусловливает конфликт между данными на выходе микропроцессора, т. е. данными, записываемыми в ОЗУ, и данными, выводимыми из ОЗУ. Чтобы предотвратить этот возможный конфликт, между выходными линиями памяти и шиной данных включается буфер с тремя состояниями типа 74LS367. Теперь, когда подан сигнал разрешения записи и память открыта, выход ее для избежания конфликта с передаваемыми из микропроцессора в ОЗУ данными блокируется посредством устройства 74LS367. Соответствующая последовательность действий показана на временной диаграмме (рис. 3.18). Ясно, что открыть ОЗУ необходимо перед выполнением операции чтения или записи данных. Однако линия разрешения записи в память находится в рабочем состоянии только тогда, когда выполняется запись данных в ОЗУ. Логическая схема для формирования необходимых управляющих сигналов приведена на рис. 3.19. Мы рассмотрели, как для одного устройства памяти в микропроцессорных системах с 3 шинами выполняются операция чтения данных из памяти и операция записи данных в память. Но шина данных микропроцессорной системы имеет 8 разря-. дов. Это означает, что одновременно должно быть прочитано или записано 8 разрядов. Так как применяемые нами блоки па- Адресная шина Aq - А Сигнал выбора памяти активен Ввод данных в память Схема 74LS367 блокирована Импульс записи в память активен Высокий уровень импульса чтения из памяти ис. 3.18. Вреыеинйя диаграмма сигналов, используемых системой во время выполнения операции записи в память. Импульс выбора памяти MEMR На вход выбора кристалла (вывод 13) устройства памяти 2102 На выводы 1,15 схем 74LS367 ис. 3.19. Использование линии выбора памяти и шины управления для получения сигналов управления ОЗУ. чяти имеют одну входную линию и одну выходную линию, не-эбходимо одновременно читать из восьми отдельных блоков ЭЗУ и также одновременно записывать данные в восемь бло-шв ОЗУ. Это достигается посредством синхронного выполнения зсех функций управления ОЗУ, т. е. подачи адреса, формирования сигналов разрешения записи и выбора кристалла. Все выводы управления восьми отдельных модулей ОЗУ соединены в виде дейзи-цепочки. Линии ввода данных соединяются с соответствующими линиями шины данных. Выходы ОЗУ подключаются к буферу с тремя состояниями типа 74LS367. Выход буфера 74LS367 подключается к входу, предназначенному для  ввода данных, того же самого модуля ОЗУ. Таким образом организуется память в виде статического ОЗУ 1 КХ8. Функциональная схема такого ОЗУ показана на рис. 3.20. 3.11. Интерфейс ОЗУ с общим входом и выходом Интерфейс ОЗУ, имеющего общий вход и выход, подобен рассмотренному выше интерфейсу ОЗУ с разделенными входом и выходом. Однако ОЗУ с общим входом и выходом имеет один вывод, используемый и для ввода данных, и для вывода данных. Это не приводит к путанице внутри блока памяти, так как очевидно, что в один и тот же момент времени можно либо читать данные из памяти, либо вводить данные в память. Устройство памяти никогда не может выполнять эти две функции одновременно. Дальнейшее рассмотрение будем вести на примере статического ОЗУ 1 КХ4 с общим входом и выходом типа 2114. При выполнении записи данных в ОЗУ 2114 общий вывод ОЗУ действует как вход. В течение времени записи выходы ОЗУ 2114 блокируются посредством внутренних схем ОЗУ. На рис. 3.21 представлены некоторые технические сведения об ОЗУ 2114. Прежде чем микропроцессор начнет подавать данные на общие выводы памяти, она должна быть подготовлена к работе, т. е. должен быть выбран соответствующий блок памяти. Чтобы избежать конфликта на внутренних выходных линиях памяти при вводе данных в ОЗУ, когда линия разрешения записи имеет уровень логического О, внутренние выводы ОЗУ блокируются с помощью внутренних схем. Указанные внутренние выходы переводятся при этом в состояние высокого сопротивления, что предотвращает возникновение какого-либо конфликта на шине данных. Это означает, что во время выполнения операции записи данных в устройство памяти 2114 в состоянии логического О должна находиться как линия разрешения записи, так и линия выбора кристалла. Это показано на временной диаграмме, изображенной на рис. 3.22. При считывании данных из ОЗУ 2114 линия выбора кристалла должна иметь состояние логического О, между тем как линия разрешения записи поддерживается в состоянии логической 1. Это достигается с помощью внешних схем. Когда линия выбора кристалла переходит в состояние логического О, данные из ОЗУ подаются на общий вход-выход. (В течение времени выполнения операции чтения из памяти общие выводы устройства 2114 играют роль выходов.) Соответствующая схема, предназначенная для формирования требуемых управляющих сигналов, представлена на рис. 3.23. Схема организации памяти, построенной из модулей ОЗУ типа 2114 для микропроцессорной системы с 3 шинами, представлена на рис. 3.24. Как

|